#### Isabel Barnola, Mark Stanovich, Michael Steurer, Karl Schoder

Center for Advanced Power Systems, Florida State University, Tallahassee, Florida Department, FSU College of Engineering, Tallahassee, Florida

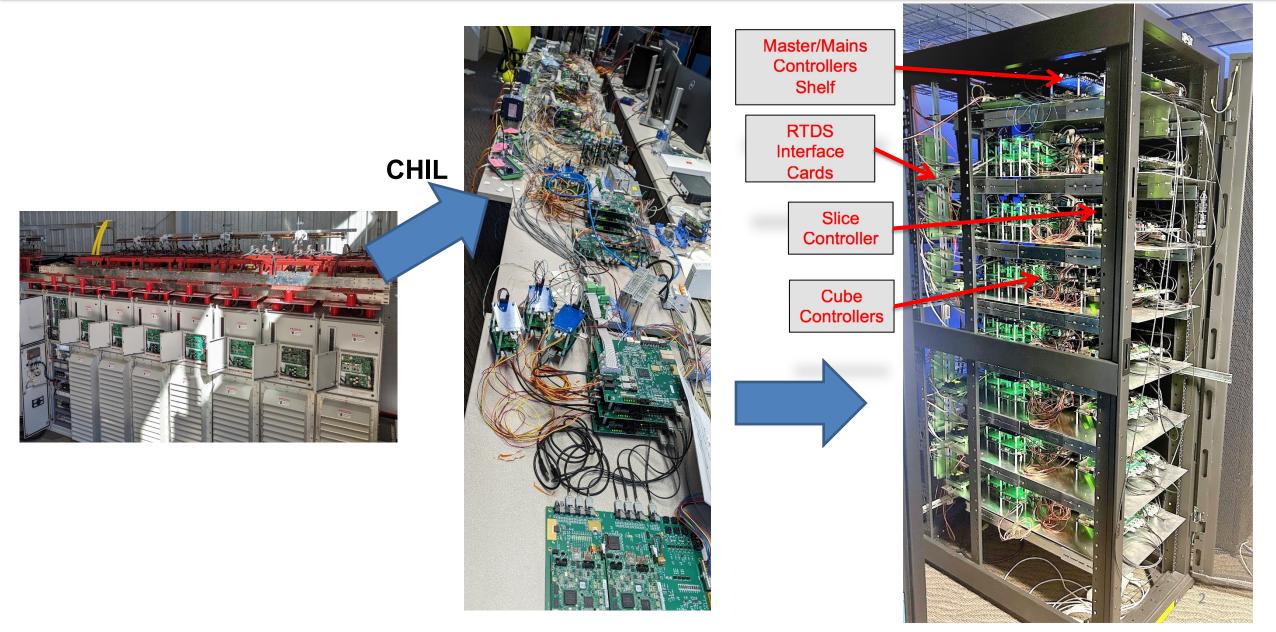

### **TECO CHIL Installation**

### Introduction

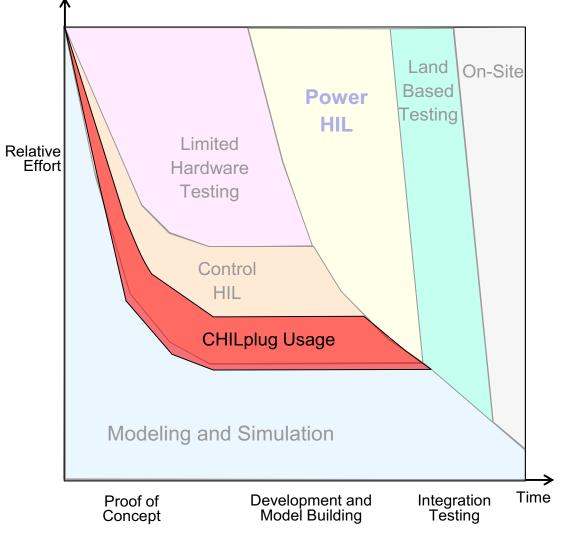

Potential CHILplug usage during the design and development process [1]

- Power electronic converter (PEC) controllers

- Controller-hardware-in-the-loop (CHIL) test

- CHIL challenges

- A need for...

- CHIL interface (the CHILplug) integrated with PEC controller

- Facilitates development and testing of controller over PEC lifetime

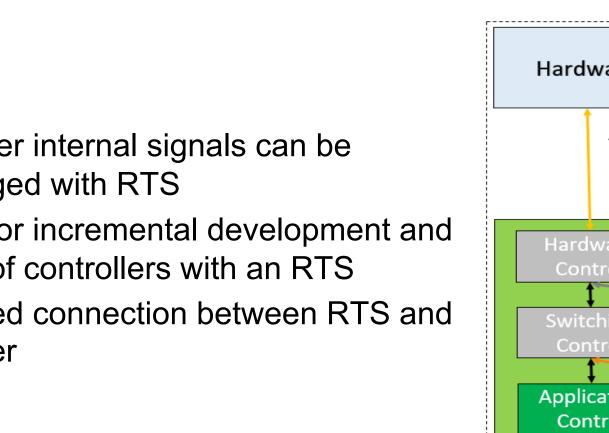

# The CHILplug concept

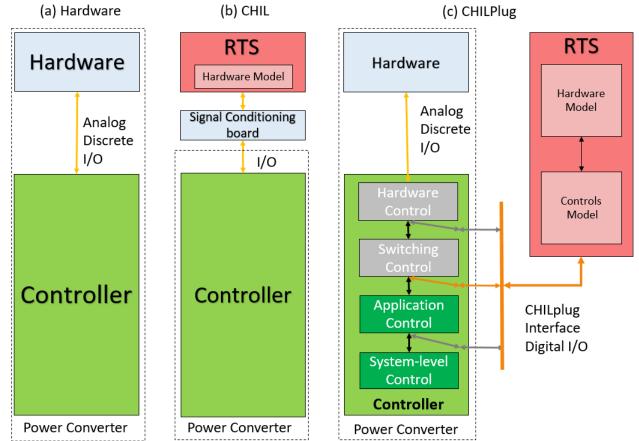

- Traditional CHIL

- Modifies PEC

- The CHILplug concept

- Dedicated computer network to/from RTS

- Testing with the CHILplug

- Software plug between PEC controller layers

#### The CHILplug concept [1]

Steurer, M., Schoder K., Stanovich M., LåΩangston J., *Interface for power systems,* U.S. Patent 11,016,452 B2 , May 25, 2021. <u>https://patents.google.com/patent/US11016452B2/en?oq=11016452</u>

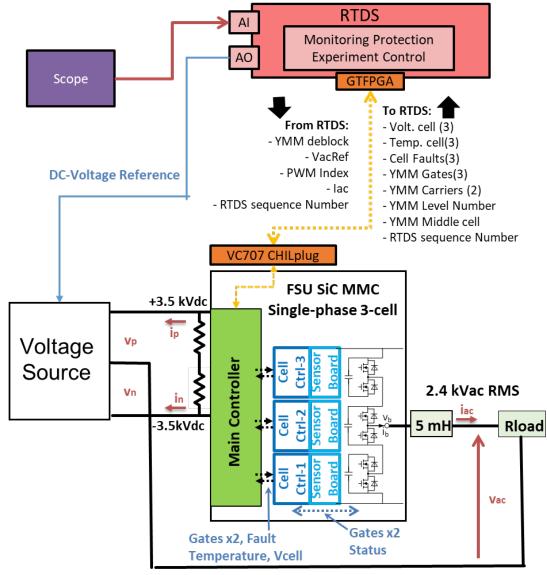

# The CHILplug

- Controller internal signals can be ulletexchanged with RTS

- Allows for incremental development and ullettesting of controllers with an RTS

- Simplified connection between RTS and controller

## **SC-MMC** Application

## Traditional CHIL setup

Traditional CHIL setup diagram

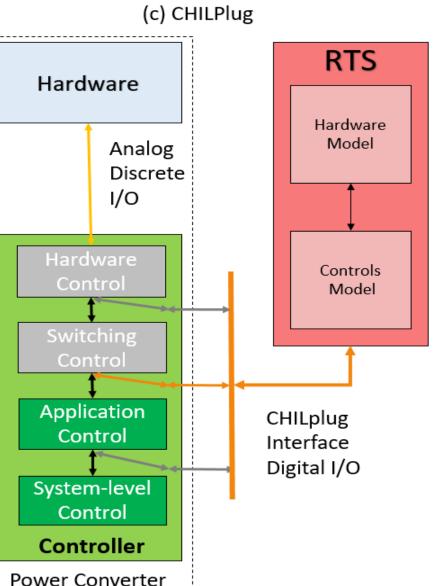

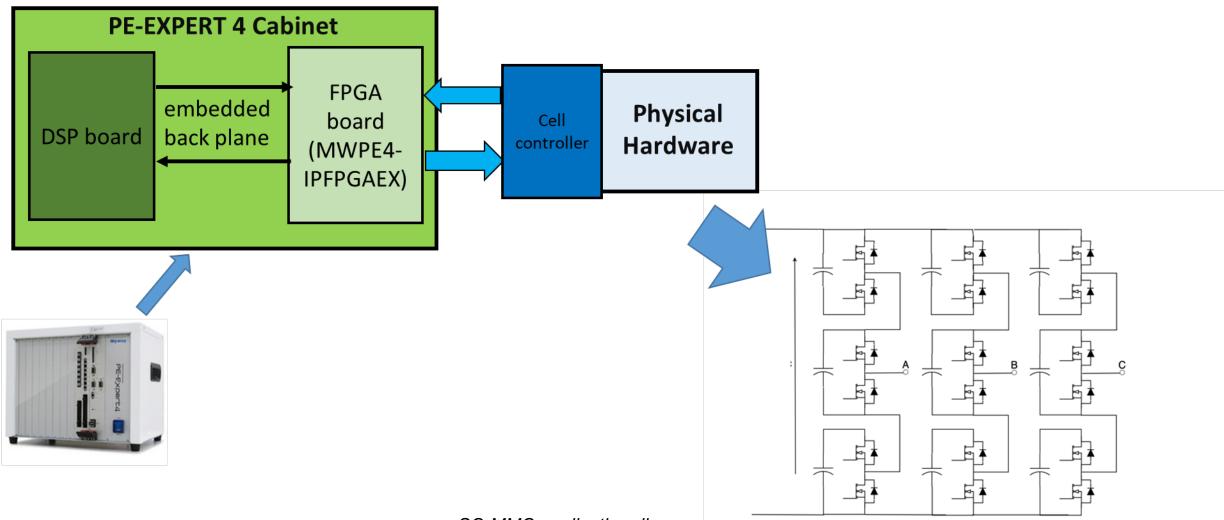

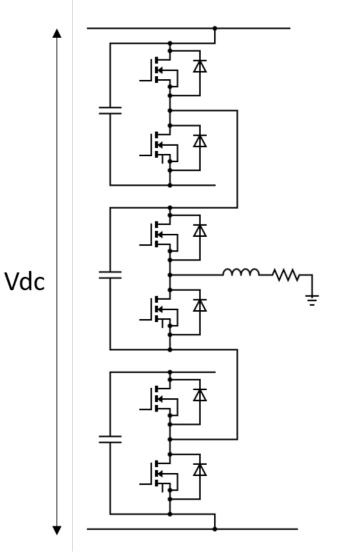

- Switched-Capacitor Modular Multilevel Converter (SC-MMC) Project

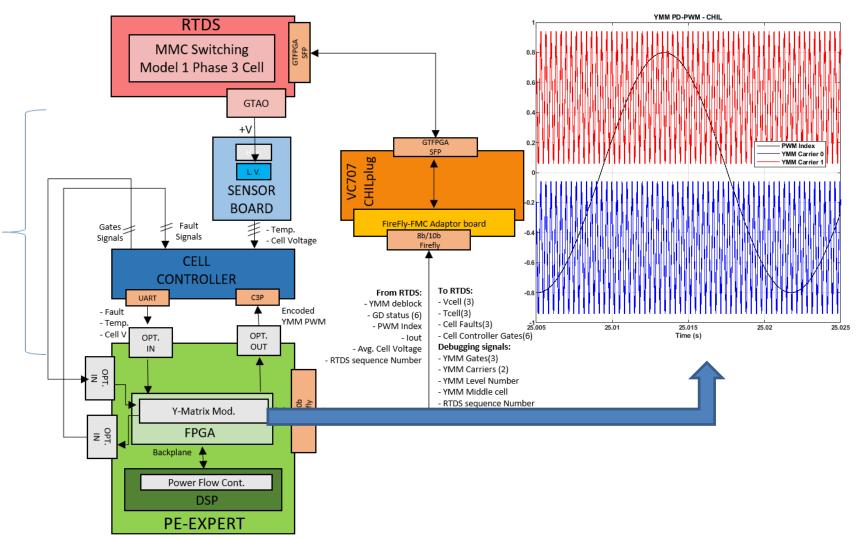

- PE-Expert controller:

- CHILplug requirements

- Minimum 1 Gbps throughput

- CHILplug interface at FPGA to be able to connect to switching control layer

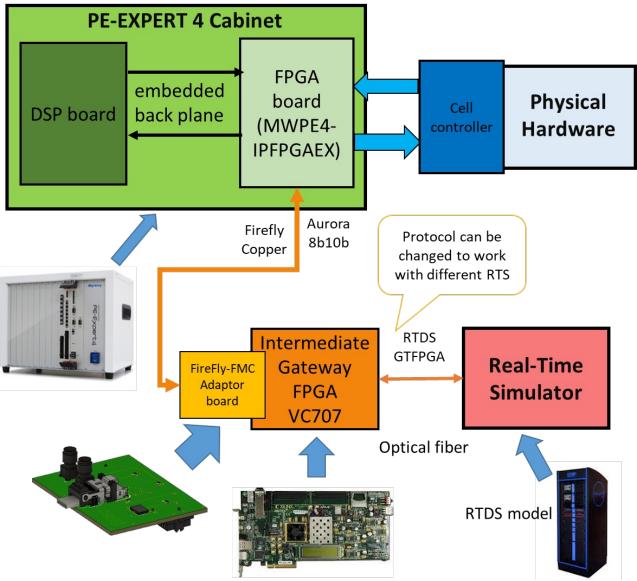

First CHILplug implementation [1]

- CHILplug interface location

- Communication at switching control layer hardware

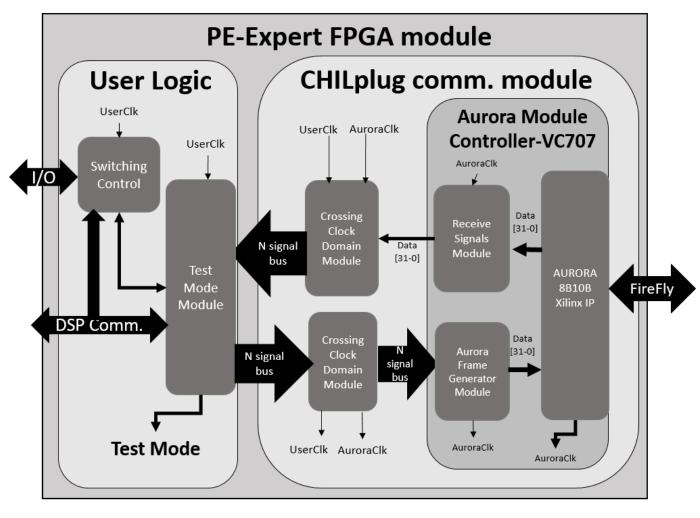

- CHILplug communication module

- Aurora 8b10b protocol at 2 Gbps

- Compatible with RTDS

- Communication channel specifications

- 32 signals of 32 bits

- Channel loopback latency for 32 signals, 2x5us time steps

CHILplug main controller's FPGA modules

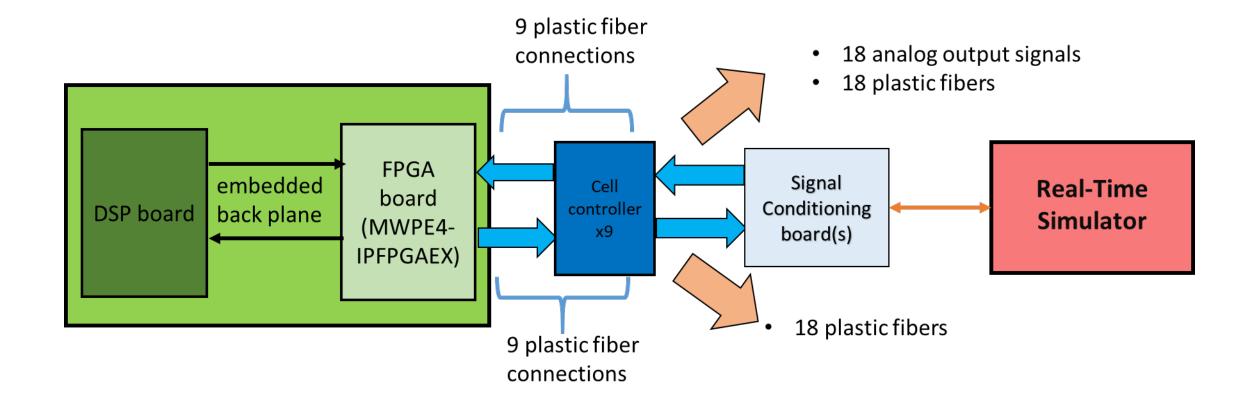

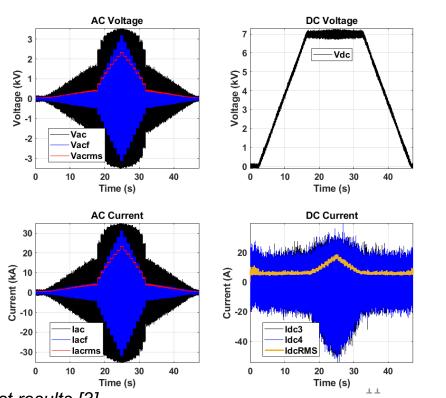

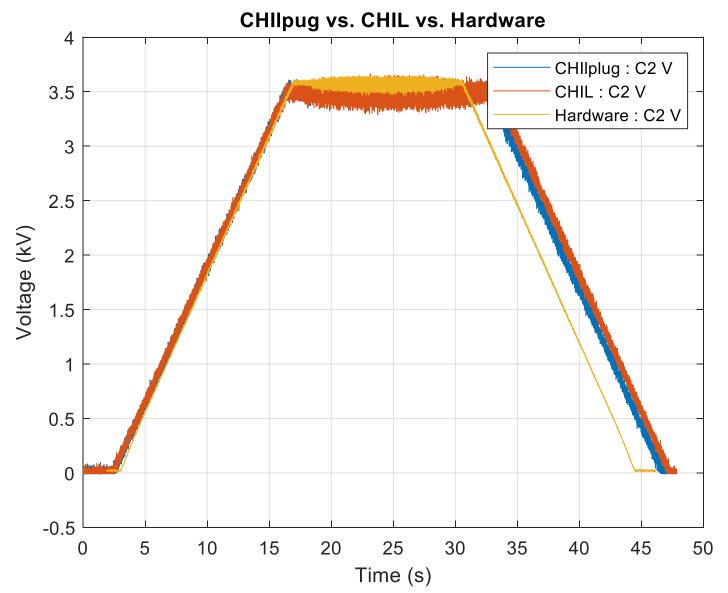

- CHILplug test setup vs. CHIL test setup vs. Hardware Setup

- Controller design for a SC-MMC operates at 4.16 kVac and a dc-bus of 7-8 kV.

- Initial tests performed for one phase open-loop to test modulation

- Utilizing Y-Matrix Modulation [2] which requires mid-cell voltage and current in order

- Development and Testing process

- 1. CHILplug testing

- 2. CHIL testing

- 3. Hardware Test

SC-MMC - single phase

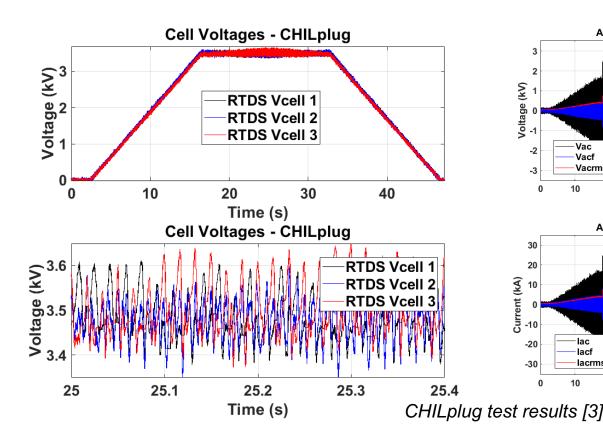

# CHILplug Test

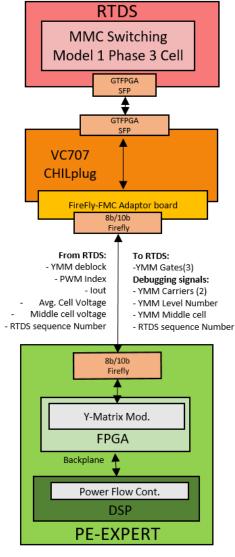

CHILplug test setup [3]

- Test purpose:

- Verify cell balancing

- RTDS model

- 1 phase of SC-MMC

- Adding cell controllers to setup x<sup>3</sup>

- Using CHILplug as debugging tool

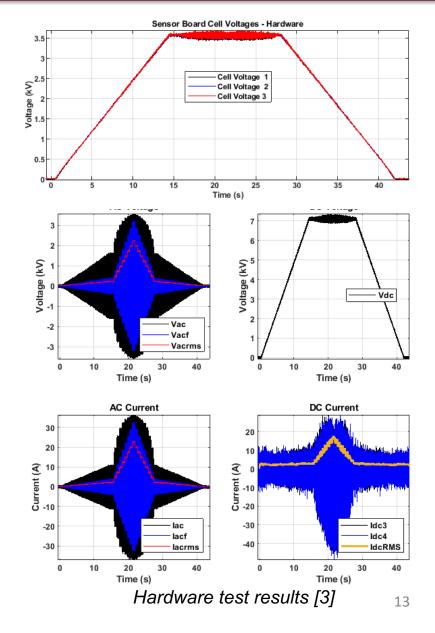

#### Hardware Test

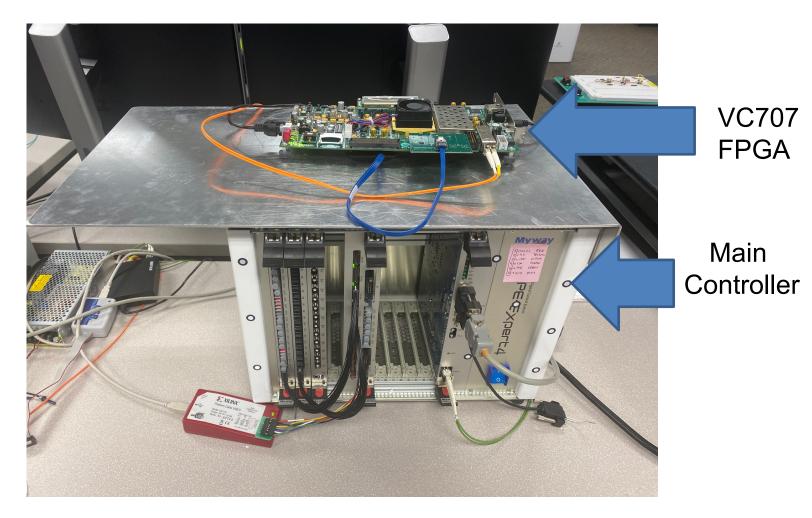

Hardware test setup [3]

#### **Result Comparison**

Middle cell voltage comparison across the different tests

- Cell controller faulty operation when added to CHIL

- Modulation previously verified using CHILplug

x3

Issue on communication interface

#### Lessons Learned

- Upfront cost

- Controller with CHIL interface compatible with RTS

- PE-Expert controller

FireFly cable issues

- Communication line rates

- CHILplug supplements rather than replaces traditional CHIL

- The CHILplug concept

- Convenient converter controller interface to RTS

- Facilitates transition between offline and CHIL development stages

- Reduces complexities in setting up a CHIL environment

- Additional benefits

- Additional high-speed interface available through all development stages for:

- Debugging

- Data recording

- Usefulness

- The CHILplug physical interface standardization to avoid costly one-off solutions

- Future work

- Establish a more rigorous definition for the CHILplug process

#### Acknowledgment:

This work was in part sponsored by the Grid DoE-AMO Application Development, Testbed and Analysis for MC SiC (GADTAMS) project.

- [1] I. Barnola, M. Stanovich, M. Steurer, K. Schoder, H. Pourgharibshahi, and R. F. Yehia, "CHILplug: Development and demonstration of a communication-based CHIL interface," ASNE AMTS, 2022.

- [2] Q. Yang, H. Pourgharibshahi, R. B. Gonzatti, S. Martin, H. Li, and F. Peng, "Modular multilevel converter with minimum arm inductance and automatic submodule voltage balance - y-matrix modulation and its theoretical proof of the automatic voltage balance," in 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 2417–2422, 2020.

- [3] I. Barnola, M. Stanovich, K. Schoder, S. Song, and M. Steurer, "SC-MMC Controller Validation Using a CHILplug Interface," IEEE ESTS, 2023.

- Patent: Steurer, M., Schoder K., Stanovich M., LåΩangston J., Interface for power systems, U.S. Patent 11,016,452 B2, May 25, 2021. <u>https://patents.google.com/patent/US11016452B2/en?oq=11016452</u>

# Thank you for your attention