## RTDS New Developments

- Cyprian Peters

- RTDS Technologies Inc.

**APPLICATIONS & TECHNOLOGY CONFERENCE 2025** CHICAGO, ILLINOIS, U.S.A.

## **RTDS STATISTICS**

- 2024: Best year ever

- Celebrated 30 years in business in 2024

- ~85 employees

- Customers in 61 countries

- >660 customers

- >2,500 NovaCor chassis sold

## **GTSOC – BLACK BOX CONTROL INTEGRATION**

- Features a powerful FPGA board with multi-processor system-on-a-chip technology to facilitate the integration of black box control models into the real-time simulation

- Vendor can provide control model to customer while protecting IP

- Similar to .dll files (PSCAD), but uses .a files to achieve deterministic real-time operation

- Connects to NovaCor through fibre cable(s)

## **GTSOC – BLACK BOX CONTROL INTEGRATION**

- Process for conversion

- Requires C code (can be original or exported from Simulink)

- Fortran code is also supported but cannot have PSCAD dependencies

- Convert C code to ".a" file with our tool

- Wrapper needs to be created to exchange signals with ".a" file running on GTSOC

- We are assisting with wrapper creation now but in the future vendors or consultants can do it on their own without our assistance or even access to RSCAD or the RTDS

| Settings Help                |  |

|------------------------------|--|

| RTDS GTSOC Interface         |  |

|                              |  |

| pols:<br>Compile Library     |  |

| Compile Library Generate BIN |  |

## **GTSOC V2 for blackbox modelling**

- 1-4 ARM cores available for black box modelling

- 1 core comes with hardware

- Additional 3 cores can be licensed

- Support for 1 fibre to communicate with all 4 cores

- Reduce number of fibre cables

- Expands the number of GTSOC units connecting to NovaCor chassis

- Supported in RSCAD FX 2.5

#### **GTSOC WEBINAR**

Learn about the GTSOC-the NEW auxiliary hardware for black box control integration with the RTDS® Simulator

#### Webinar & demo

#### The GTSOC: Black Box Control Integration with the RTDS Simulator

Date: Wednesday, November 23, 2022

Time: 9:00 AM Winnipeg (CST)

Location: Online

#### What to Expect

A discussion on the relavance and benefit of black box control integration

- An overview of the new GTSOC and its capabilities

- Hear from SMA on the implementation of their controls on the GTSOC

A screen-capture simulation demo using the SMA controls

#### Webinar description

Join us for a free webinar on exciting new capabilities in realtime simulation: the inclusion of black box control models. The GTSOC, a new auxiliary hardware for the RTDS Simulator, facilitates the deterministic integration of vendor control models into the real-time power system simulation while protecting intellectual property. The GTSOC features a powerful FPGA board with multi-processor system-on-a-chip technology to support this challenging application. The ability to black-box vendor controls and include them in a hardwarein-the-loop testbed is increasingly important for interoperability testing and de-risking inverter-based resources on the modern grid.

This webinar will include a demonstration in collaboration with SMA Solar Technology AG, an inverter vendor. A black box version of SMA's proprietary controller has been implemented on the GTSOC. In the demo, watch how the GTSOC running SMA's controls is used to control battery energy storage system (BESS) inverters in the real-time simulation.

#### **2025 APPLICATIONS & TECHNOLOGY CONFERENCE**

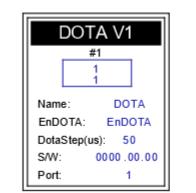

## **DOTA V1 for blackbox modelling**

- Updated DOTA component

- Available in RSCAD FX 2.5

- Supports new features

- Case stop signal sent from GTSOCv2

- Support use of DOTA in breakpoint mode and non real time mode

- Reduced data transfer time

- Support loading binary file or additional parameter files

- Terminate function

- Pointer function include for inter-core communication

- Use of DOTA V1 requires updated version of blackbox builder tool

#### **New GUI: Blackbox Builder 2.0**

| H Blackbox Builder - Version 2.0 |                                                                                             |                                      |                                         | – 🗆 ×   |

|----------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------|---------|

| File Edit Tools Help             |                                                                                             |                                      |                                         |         |

| 🗅 🛅 🕑 💭 🎧 🐨 🗡 Name               | Welcome Library Builder Test ×                                                              |                                      |                                         |         |

| Name                             |                                                                                             |                                      |                                         |         |

| ,<br>,                           | Test.project X                                                                              |                                      | L .                                     |         |

| •                                | Firmware Generation                                                                         |                                      | Library Manager                         |         |

| •                                | Project Name: Test                                                                          | Enable Inter-Core Communication      | Application Libraries:                  |         |

| ▶                                | Compile Targets GTSOC V1 GTSOC V1 SingleFiber G GTSOC V2 GTSOC V2 SingleFiber Use Date/Time |                                      | Import Library Files AutoLoad Libraries | Log All |

|                                  |                                                                                             |                                      | Header Files For Selected Library:      |         |

|                                  | Core 0 × Core 1 Core 2 Core 3                                                               |                                      | Import Header Files                     |         |

|                                  | use a file  Vumber of Instances 1                                                           | Summarize All Settings               |                                         |         |

| •                                | Vendor ID(0x): 0000 App ID(0x): 00 App Ver(0x): 00 Print Debug                              |                                      |                                         |         |

| •                                | App Library: + *                                                                            |                                      |                                         |         |

| •                                |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  | Wrapper:                                                                                    | Set / Browse Clear Import Template 👻 |                                         |         |

|                                  | Compiler Flags for Wrapper (optional): + Show All Compiler Flags                            |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  | Library Flags (optional): + Show All Library Flags Reset                                    |                                      |                                         |         |

|                                  | ▼ Library Flags                                                                             |                                      |                                         |         |

|                                  | m                                                                                           |                                      |                                         |         |

|                                  | stdc++                                                                                      |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  | Build Firmware (All Enabled Cores / Selected Compile Targets)                               |                                      |                                         |         |

|                                  |                                                                                             |                                      | I                                       |         |

|                                  | Output Window Clear Output Show Commands                                                    |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

|                                  |                                                                                             |                                      |                                         |         |

- Lighter Version

- No longer requires Vitis

- Significantly reduces disk space requirements

- Generates .a file

- Create GTSOC firmware

- Available to share

- Previous Blackbox builder still available

- Vitis has benefits

- Supports DOTA V1 component only

## **GTSOC V2 – AURORA MUX**

- Provides additional Aurora ports for a NovaCor chassis

- 1 to 4 setup, ( 4 to 16)

- 64 inputs/outputs per stream

- 4 streams included with hardware

- 2Gbit and 3.125 Gbit line rates supported

- Each additional set of 4 streams can be licensed

- Same cost as NovaCor Aurora license

| Al           | JR | DRA | ٩M | UX |

|--------------|----|-----|----|----|

| GTIO Port: 1 |    |     |    |    |

| Ch           | #1 | #2  | #3 | #4 |

| То           | 0  | 0   | 0  | 0  |

| Fr           | 0  | 0   | 0  | 0  |

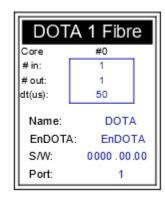

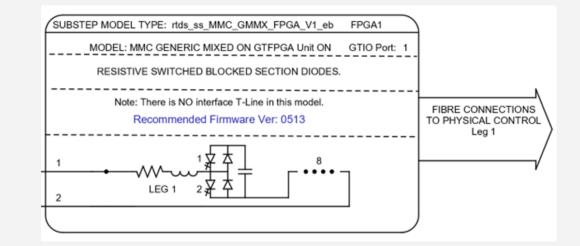

## **Embedded MMC Valve Models**

- MMC-HVDC valve models run on the FPGA in the GTSOC auxiliary hardware

- In the past, traveling wave T-lines were used as an interface, 0.5 or 1 timestep delay

- Increases in simulation timestep caused a corresponding increase in T-line length

## **Embedded MMC Valve Models**

- Recent updates have removed the need for a T-line interface

- Models can now be used in the main timestep environment

- Both GMMX and U5 components are available as embedded models in both mainstep and substep

- Embedded GMMX and MMC5 also includes an optional battery model

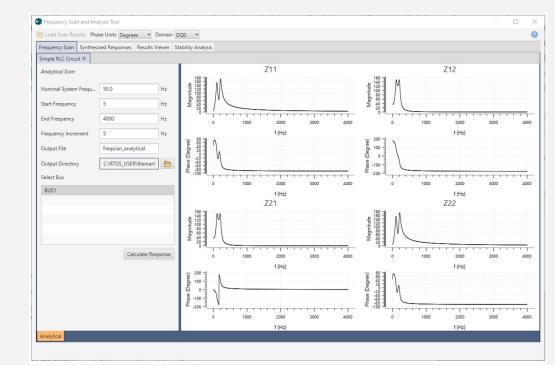

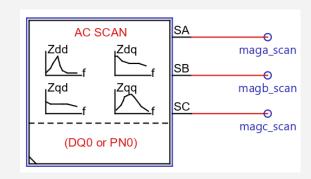

## **FSAT Component**

#### **Analytical based**

• Offline

#### Measurement based

- Online

- Injects harmonics to a system in equilibrium

- Small signal multi-sine perturbation

- Measures the harmonic current and voltage for the subsystem

- Computes Discrete Fourier Transform (DFT)

#### **Stability Analysis**

- Import Scan Results

- Create Bode Plot

#### Analytical Scan

#### Frequency Scan Component

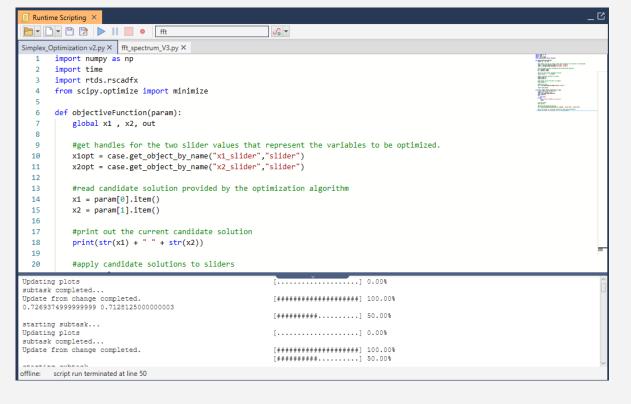

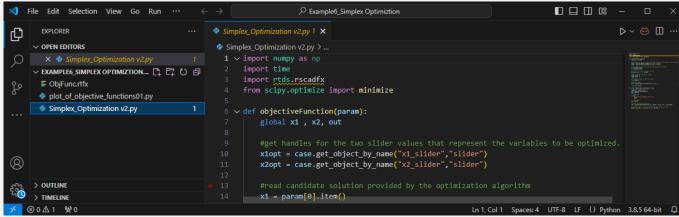

# **Python Scripting**

- Python Scripting API was just released in RSCAD FX 2.4

- Allows Users to Automate Tasks

- Running Simulations

- Gathering Results

- Modifying Simulation Cases

- Ability to Leverage Python Packages

- Matplotlib

- numpy

- scipy

- PyTorch etc.

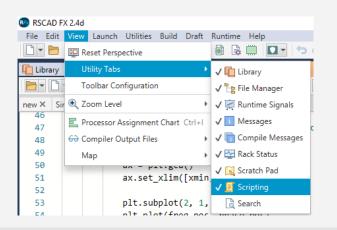

# **Python Scripting**

- Runtime Scripting Utility Tab

- Used to Write, Record and Run Scripts

- Can be used for Python and Legacy Scripts

- External IDE Support

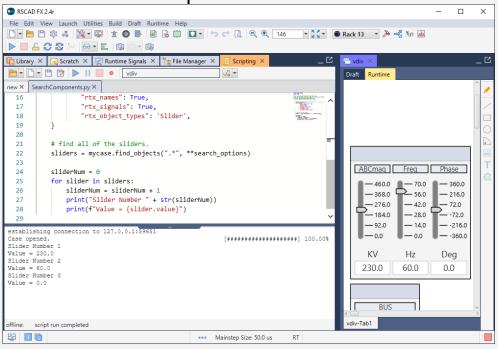

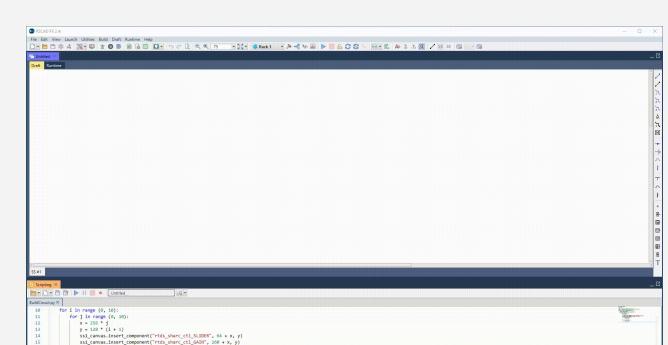

# **Python Scripting**

- Build Circuits

- Automatically Place Components on Canvas

- Search for Components •

ss1\_canvas.insert\_component("wirelabel", 256 + x, y)

ss1 canvas.create wire(1, [

(96 + x, y),

(128 + x, y),

**AMETEK**

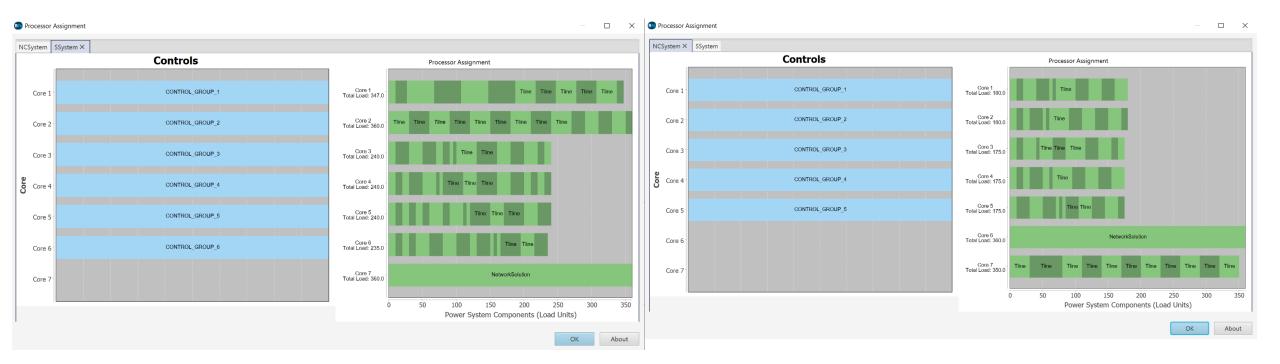

### **ENHANCED NON-REAL TIME SIMULATION**

#### Available on NovaCor 2.0

- Enhanced simulation capacity when using non-real time simulation

- 3600 Load Units PLUS 360 nodes per core (approximately 10 times real time capacity)

- Execution time per timestep is minimum 200µs, regardless of load

- Execution time will automatically adjust above 200µs to accommodate load

### **REAL WORLD EXAMPLE – LARGE UTILITY CASE**

**2025 APPLICATIONS & TECHNOLOGY CONFERENCE**

RTDS APPLICATIONS &

## **REAL WORLD EXAMPLE – LARGE UTILITY CASE**

- Case includes several HVDC bipoles with full internal controls

- Runs on 14 cores in real time with a timestep of 47 microseconds.

- An offline case that is very similar runs on 3 cores on a high-end computer at 50 microseconds

- The offline case requires 120 seconds for 1 second of simulation

- The RTDS case in non real time mode fits on 1 core

- It runs at 50 microseconds at 5.6 times real time (>20 times improvement!)

- Or over 60x considering 1 vs. 3 cores

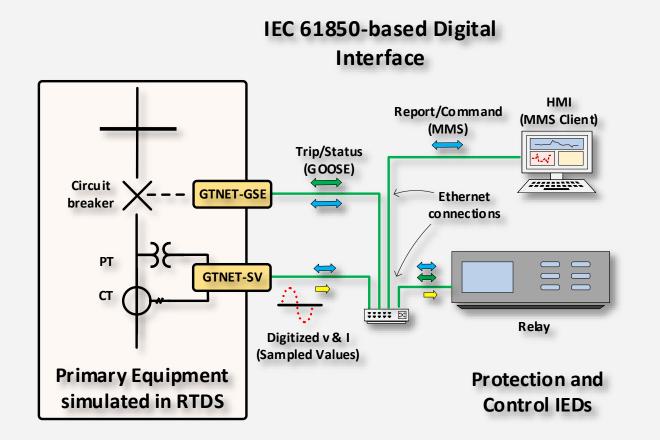

### **TYPICAL IEC 61850 WITH GTNET GSE/SV**

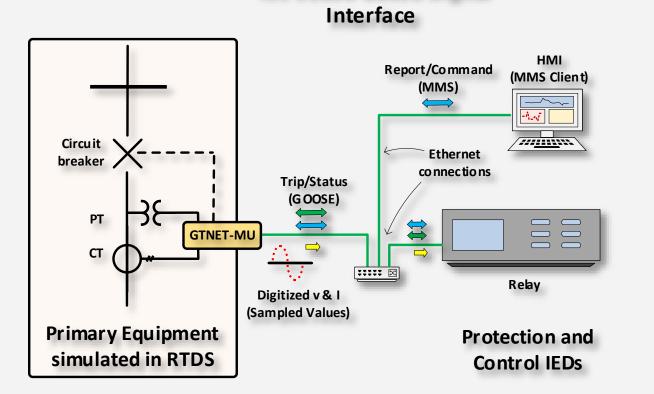

### **IEC 61850 WITH MERGING UNIT FIRMWARE**

IEC 61850-based Digital

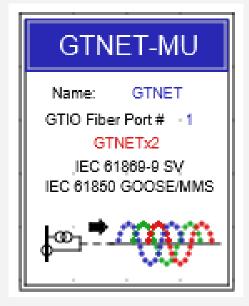

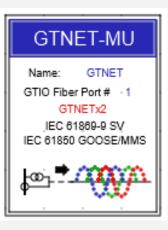

### **GTNET-MU**

- GTNETx2 hardware already supports IEC 61850 GOOSE, SV and MMS functionalities

- GTNET-MU implementation provides the GOOSE, SV and MMS simultaneously, mimicking the operation of Process Interface Units

This integration allows our users to minimize the use of GTNETx2 hardware and reduce the required no. of Ethernet connections

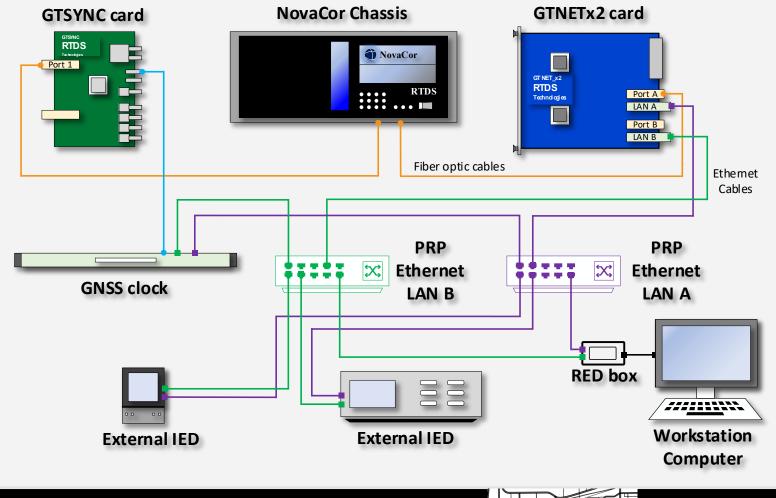

## PARALLEL REDUNDANCY PROTOCOL

- IEC 62439-3: 2016 defines Parallel Redundancy Protocol (PRP)

- Provides **zero** recovery time for time-critical applications

- Uses two independent parallel networks of any topology

- Duplication of the network: LAN A and LAN B

- Network may contain normal switches (except for IEEE 1588 or IEC/IEEE 61850-9-3 PTP, which requires special switches)

- Data frame last 16-bit tag identifier: 0x88FB

- Each PRP node sends periodic (typically every 2 s) supervision frames

### **PRP CONNECTION OF GTNETx2 CARD**

**2025 APPLICATIONS & TECHNOLOGY CONFERENCE**

**CHICAGO, ILLINOIS** Technologies

AMETEK

### **PRP SUPPORT GTNETx2 FIRMWARE FEATURES**

- Supports all 9 GTNET protocols

- Requires entire GTNETx2 card

- Both Ethernet LAN transceivers of a GTNETx2 card to obtain two redundant network connections (LAN A and LAN B)

- In order to enable network redundancy support, select the "PRP" option under "Network Redundancy"

- Supported in GTSOCV2 SV (8 streams)

- available in RSCAD FX 2.5

| Edit Card Parameters (Port:1 Card:GTNETx2_MU) X |              |                |                                                                                         |  |  |

|-------------------------------------------------|--------------|----------------|-----------------------------------------------------------------------------------------|--|--|

|                                                 |              |                |                                                                                         |  |  |

|                                                 | IP Address:  | Subnet:        | Gateway: SNTP Server IP:                                                                |  |  |

| Primary                                         | 10.103.41.31 | 255.255.254. 0 | 10.103.40.1 0.0.0.0                                                                     |  |  |

| Alias 1                                         | 10.103.41.32 | 0. 0. 0. 0     |                                                                                         |  |  |

| Alias 2                                         | 10.103.41.33 | 0. 0. 0. 0     |                                                                                         |  |  |

| Alias 3                                         | 10.103.41.34 | 0. 0. 0. 0     |                                                                                         |  |  |

| Alias 4                                         | 10.103.41.35 | 0. 0. 0. 0     | Gateway / SNTP Server                                                                   |  |  |

| Alias 5                                         | 10.103.41.36 | 0. 0. 0. 0     | Is Common<br>For Entire                                                                 |  |  |

| Alias 6                                         | 10.103.41.37 | 0. 0. 0. 0     | GTNET Card                                                                              |  |  |

| Alias 7                                         | 10.103.41.38 | 0. 0. 0. 0     |                                                                                         |  |  |

| Alias 8                                         | 10.103.41.39 | 0. 0. 0. 0     |                                                                                         |  |  |

| Alias 9                                         | 10.103.41.40 | 0. 0. 0. 0     |                                                                                         |  |  |

| Use Primary<br>Subnet For<br>All Aliases        |              |                | Network RedundancyDisable*Reset GTNET card for networkredundancy changes to take effect |  |  |

| OK Close                                        |              |                |                                                                                         |  |  |

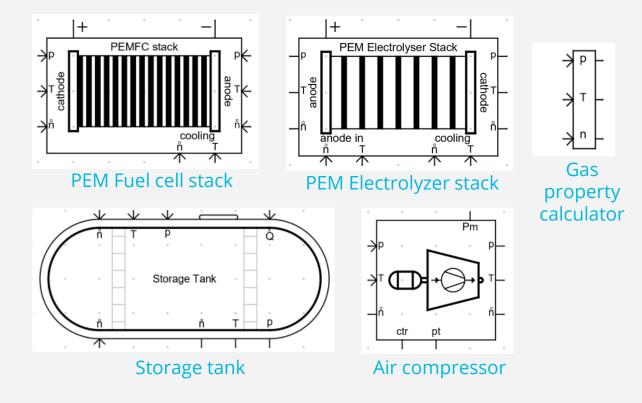

# **Multi Energy Flow Simulation**

#### Hydrogen System Models and Example Cases

• Simulating electrical behavior and the thermodynamic behaviors.

| • 6 | xample Cases                                     |

|-----|--------------------------------------------------|

|     | Name                                             |

| •   | 05 Energy Storage Systems                        |

| ►   | Battery Systems                                  |

| ►   | FlyWheel and Pumped Storage Systems              |

| ►   | E Fuel Cells                                     |

| •   | MEF                                              |

|     | MEF_ELZ_H2production                             |

|     | 🗋 ELZplant.jpeg                                  |

|     | 🔀 MEF - Hydrogen Production via Electrolysis.pdf |

|     | MEF_ELZ_H2production.rtfx                        |

|     | <ul> <li>MEF_FCplant2grid</li> </ul>             |

|     | 🗋 H2powerplant.jpg                               |

|     | MEF - Fuel Cell Power Generation.pdf             |

|     | HEF_FCplant2grid.rtfx                            |

|     |                                                  |

## Multi Energy Simulation - Webinar

- Recently provided webinar on Multi Energy simulation application

- https://www.rtds.com/news-and-events/rtds-events/webinars/webinarempowering-hydrogen-energy

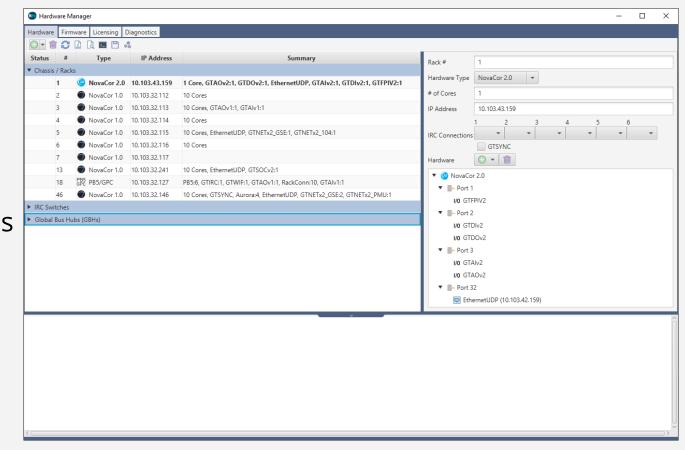

## RSCAD FX Enhancements – Hardware Manager

- Single integrated tool to manage all your RTDS hardware. Integrates:

- Config\_file Editor

- Firmware Upgrade Utility

- Global Bus Hub Configuration tools

- Diagnostics

- User friendly interface

- Includes integrated SSH terminal for advanced diagnostics

- Increased speed when updating firmware for multiple racks simultaneously

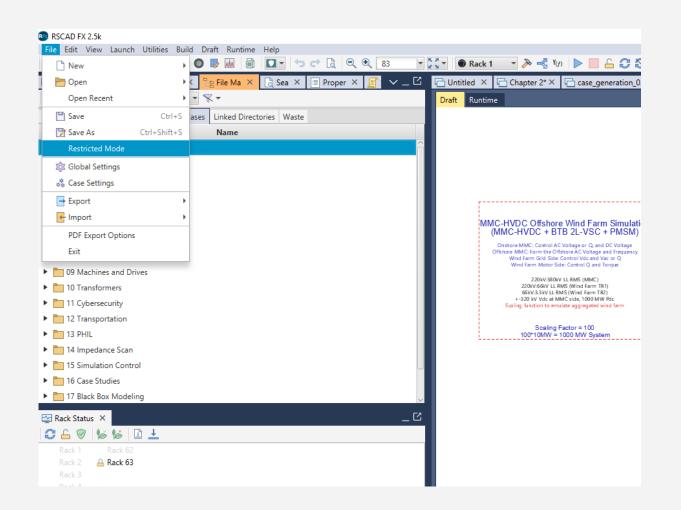

### **RSCAD FX Enhancements – Restricted Mode**

- In Restricted Mode, DRAFT cannot be modified by the user

- Prevents changes from been made by users not authorized to modify the case

- Password protected

- RUNTIME can be modified as usual

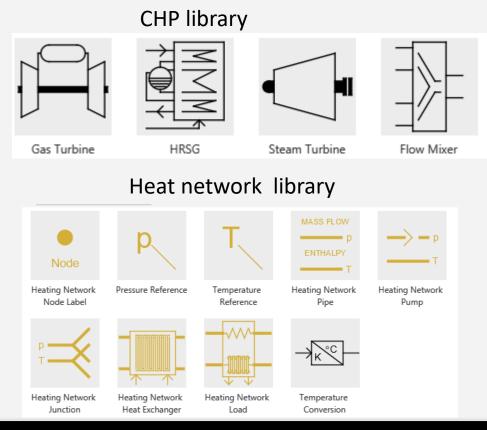

# **Multi Energy Flow Simulation**

#### **Combined Heat and Power (CHP) and Heat Network Components**

- Integrates heating and electrical networks

- Investigate thermal-electrical interactions

- New MEF components added to the library

## **RSCAD FX 2.5 Enhancements**

- Thermal heat networks, include thermal hierarchy box, numerous new components, documentation and example cases

- 3PH scaling transformer

- 3PH TDM multi winding transformer

- New DOTA component and updated example cases

- Single fiber DOTA component

- Aurora improved firing pulse GTFPGA component

- GTSOC-SV PRP support

- New relay interface tutorial chapter

- EV Powertrain example

- PDC python example

## **RSCAD FX 2.5 Enhancements**

- Resize RunTime components

- RunTime Groups have been introduced

- Snap to grid for Runtime Shapes

- Container minimizing (basically plot and frame containers can now be minimized)

- Component properties utility pane

- Improvements in handling runtime shapes resize and move

- A number of bug fixes have been made

# **Ongoing Developments in 2025**

- Multiplot rewrite for RSCAD FX

- 61850 ICT tool will be looked to have a more simplified operating mode

- 61850 ICT tool to support more features

- GTNETx2 clients MODBUS first then DNP/104 to follow

- Modbus- 2 clients, Connect to up to 20 Modbus Servers (outstations)

- New GUI for configuration

- GTECAT support EtherCAT communication

# **Ongoing Developments in 2025**

- A new serial communication I/O card is under development (GTSIO)

- Card will support

- CAN 2.0

- RS232-C

- RS485

- USB 2.0

- I2C

- SPI

- Ethernet (UDP) protocols

- 19" rack mounted

- Connects to NovaCor chassis via fibre cable

## **2025 EVENTS**

| Event               | Location                  | Date           |

|---------------------|---------------------------|----------------|

| DPSP APAC           | Hong Kong                 | January 8 – 11 |

| ACDC Global         | Birmingham, UK            | March 17 - 19  |

| DistribuTech        | Dallas, USA               | March 25 - 27  |

| Microgrid Knowledge | Dallas, USA               | April 15 – 17  |

| ACPEE               | Beijing, China            | April 15 – 19  |

| CIGRE NRCC          | Trondheim, Norway         | May 12 - 15    |

| RTDS ATC            | Chicago, USA              | May 6 – 8      |

| CIGRE ERIAC         | Cuidad del Este, Paraguay | May 25 – 29    |

| IPST                | Guadalajara, Mexico       | June 8 – 12    |

| PEMD                | Nottingham, UK            | June 11 - 12   |

## **2025 EVENTS**

| Event                 | Location            | Date                     |

|-----------------------|---------------------|--------------------------|

| CIRED                 | Geneva, Switzerland | June 16 - 19             |

| PAC World Global      | Glasgow, Scotland   | June 23 - 26             |

| PowerTech             | Kiel, Germany       | June 29 – July 3         |

| IEEE PES GM           | Austin, USA         | July 27 - 31             |

| University Conference | Tianjin, China      | August                   |

| CIGRE Symposium       | Montreal, Canada    | September 29 – October 2 |

| ECCE                  | Philadelphia, USA   | October 18 - 23          |

| APAP                  | Phoenix Island Jeju | October 20 - 24          |

| WPRC                  | Spokane, USA        | October                  |

| China UGM             | Beijing, China      | ТВА                      |

| IEEE PES GTD          | Bangkok, Thailand   | November 27 - 29         |

|                       |                     |                          |

2025 APPLICATIONS & TECHNOLOGY CONFERENCE

#### **TRAINING COURSES IN WINNIPEG**

March 10 - 14: Introductory Training Course March 17 - 21: Advanced Applications – Renewable Energy & Microgrid Applications

Fall 2025: Intro + GTNET and P&A applications

Spring 2026: Intro + HVDC, FACTS and Power electronic applications

\*\*Off-site training course in Dubai in Q4 2025\*\*

#### **WEBINARS**

Our 2024 webinars were very well attended! We had an average of 150 people attend our webinars either live or on demand.

6 webinars for 2025