# **GPES**

## Fast and powerful FPGA-based power electronics solver

The general power electronics solver (GPES) supports the real time modelling of power electronics on the RTDS Simulator's GTFPGA Unit. The dedicated, FPGA-based hardware which runs GPES is capable of high-density calculation in parallel with the power system simulation running on the central RTDS Simulator processing hardware.

GPES provides a highly flexible platform for modelling large power electronics circuits and custom converter topologies at a reduced timestep.

GPES can run with either NovaCor or PB5-based simulation hardware.

### Larger Networks: Increased Power and Efficiency

Each GTFPGA Unit running GPES can support up to 128 nodes and 256 branches

The GTFPGA Unit's enhanced computational abilities mean that many more nodes and switches can be modelled than is possible with a regular small timestep subnetwork. This is advantageous for large power electronic circuits which would otherwise need to be modelled on multiple cores or processors, requiring potentially problematic interface transmission lines within the model.

#### **Smaller Timesteps: Greater Accuracy**

GPES can run power electronics circuits with timesteps in the sub-microsecond range

GPES uses the same LC modelling approach as the small timestep subnetworks, but running on the dedicated GTFPGA Unit means a significantly reduced timestep is possible. For large or custom topology circuits, this means lower losses and acceptable performance over a higher range of switching frequencies.

#### Interfacing with the Simulation and External Equipment

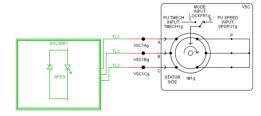

The GTFPGA Unit running GPES is connected to the RTDS Simulator via a fiber optic cable.

FPGA-based GPES network development is done within a bridge box which is connected to a model running in the small timestep on the main simulation hardware. In this way, the GPES circuit can exchange control signals, inputs and outputs with the main simulation.

GPES has an Aurora interfacing block that allows firing pulses to be received by GPES directly from external controls. The external device is connected via fibre cable to the front of the GTFPGA Unit.

Learn more at www.rtds.com/GPES