# RTDS RTDS NEWS Technologies

# **WHAT'S NEW: MARCH 2018**

Introducing TWRT: test traveling wave protection devices with small timestep frequency dependent lines

The all-new GPES allows custom converter modelling in the nanosecond range via FPGA

#### Upcoming Training Courses

**RTDS Simulator Introductory Training Course** September 24 - 28, 2018

Advanced Applications: TBA October 1 - 5, 2018

Watch our website for registration details!

# **Upcoming Events**

### **IEEE PES T&D**

Denver, CO, USA April 16-19, 2018

> Join us at Booth 1250 and don't miss our seminar on traveling wave testing:

> > **Session PSS29**

#### **PAC World**

Sofia, Bulgaria June 25-28, 2018

#### **IEEE PES GM**

Portland, OR, USA August 5-10, 2018

#### RTDS European UGM Genk, Belgium

Keep an eye on rtds.com for our call for abstracts!

#### SPOTLIGHT: NEW FEATURE

# Harder, better, faster, stronger: Test ultra high-speed traveling wave protection with the all-new TWRT

The emergence of traveling wave fault location is a breakthrough in line protection, improving power system performance, transient stability margins, and public safety, and limiting equipment damage. The new, ultra-highspeed protective devices using these algorithms can locate faults with unprecedented accuracy, recording events in the MHz sampling rate range and tripping securely in a few milliseconds. Now, for the first time ever, the RTDS Simulator offers a platform for testing travelling wave protection devices in a closed loop.

SEL's new T400L (Time Domain Protection) connected in the loop with TWRT

The TWRT (Traveling Wave Relay Testing) platform is RTDS Technologies' response to the emergence of traveling wave protection devices on the market and the change that these devices will bring for utilities worldwide. TWRT is a simulation environment that can run on the main RTDS Simulator hardware—either a NovaCor™ processing core or a PB5 processor—or on the GTFPGA Unit. When

running on NovaCor or PB5, larger test circuits such as parallel line schemes can be simulated. The GTFPGA Unit running the TWRT platform as a firmware provides a lower-cost option for simulating smaller circuits. This flexibility allows customers using different versions and quantities of RTDS Simulator hardware to use TWRT in varying capacities. As with all models and features running on the main simulation hardware, TWRT will be readily available for use by users with the latest version of RSCAD.

At the heart of TWRT is a frequency dependent transmission line model operating at a very small timestep, allowing the RTDS Simulator to accurately represent the attenuation of the traveling wave as it moves along the line. Eliminating the use of Bergeron models to represent lines or to provide an interface ensures attenuation and dispersion for proper performance analysis of traveling wave protection and fault locating.

TWRT's frequency dependent transmission lines are the most robust and flexible models on the market. The models feature multiple line segments, allowing the user to represent physical transposition and to place faults at multiple different locations.

Watch the TWRT launch video at www.rtds.com/twrt.

#### Don't miss the Protection & Automation Suite...

The all-new Protection and Automation Suite (PASuite) is a standalone program launched from RSCAD that can communicate with the RTDS Simulator's GTNET/GTNETx2 card or other external devices compatible with a variety of modern substation automation protocols, as follows: IEC 61850 MMS servers, DNP3 masters or outstations, IEC 60870-5-104 masters, and MODBUS masters.

Learn more at www.rtds.com/PASuite

#### ... or enhancements to small timestep subnetworks

RTDS Technologies has implemented performance enhancements to the small timestep bridge box for NovaCor™. The following limit increases will allow users to simulate larger and more complex small timestep networks in each bridge box.

- Node limit increased to 45

- Number of signal inputs increased to 47

- Number of resistive switches increased to 10

- Number of monitoring outputs increased to 96

#### SPOTLIGHT: NEW FEATURE

# Swing low, sweet timestep: Model custom power electronics in the nanosecond range with GPES

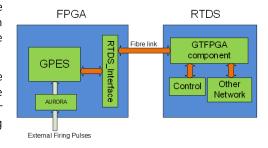

The all-new general power electronics solver (GPES) supports the real time modelling of power electronics on the RTDS Simulator's GTFPGA Unit. The motivation behind the development of the GPES is to provide a highly flexible platform for modelling custom converter topologies with a

reduced time step. The dedicated, FPGA-based hardware which runs GPES is capable of high-density calculation in parallel with the simulation running on the central RTDS Simulator hardware. Each GTFPGA Unit running GPES can support up to 128 nodes and 256 branches.

GPES uses the same LC modelling approach as the small timestep subnetworks (VSC bridge box) solved on the NovaCor's processor – however, the GTFPGA Unit's enhanced computational abilities mean that more nodes, more switches, and a reduced timestep are possible. The smaller time step will result in smaller L and C values for ON and OFF switching state representation which will result in more accurate representation of the switching losses for freely configurable converters.

Similarly to the small timestep subnetwork environment, GPES network development is done within a special GPES bridge box component in RSCAD. The new GPES tab in the Master Library contains a limited selection of components that can be used within the GPES bridge box. The GPES bridge box connects to a small timestep bridge box running on a NovaCor or PB5. That means the circuit running

on GPES can be connected to a model running in the small timestep and exchange control signals with the small timestep. This way, any components required in the case which cannot be modeled on GPES

(e.g. machines or dynamic loads) can be modelled in the small timestep as shown below. The GPES also has an Aurora interfacing block that allows firing pulses to be received directly from external controls.

The GTFPGA Unit running GPES is connected with the main RTDS Simulator hardware via fibre cable (connected from the rear of the GTFPGA Unit to the rear of the NovaCor chassis or GTWIF-based rack running the simulation).

## **New Features in RSCAD**

- Added the Protection and Automation Suite, Generic Power Electronics Solver (GPES), and small timestep subnetwork enhancements. Read more about these above.

- RunTime plots can now be saved to .csv (comma separated values) type files.

- Added support for underscore(\_) characters to be used in signal names, component names, etc.

- GTNET-SKT sample case added Closed loop communication between RTDS and a Raspberry PI.

- The single phase and three phase dynamic PQ injection models \_rtds\_PQinject.def and \_rtds\_spPQinject.def

have been modified to included rate limits for changing the control setpoints. The three phase PQ inject model

includes a load flow section.

You can access the full RSCAD release notes in the Client Area at support.rtds.com/clientarea/.

If you have an idea for a new feature, please send it to feedback@rtds.com. We want to hear from you!