#### Your world in real time.

#### **IIIRTDS** Technologies

RTDS.COM

# Modelling of DC Breakers

RTDS Technologies Inc. User's Groups Meeting 2019 China

# Outline

Types and Operating Modelling and Simulation

Conclusion

# **DC Breaker Types**

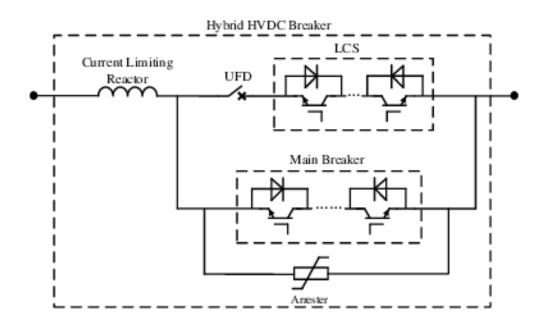

- ✤ Hybrid Breaker

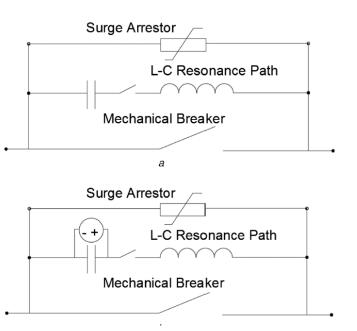

- Mechanical Resonant Breaker

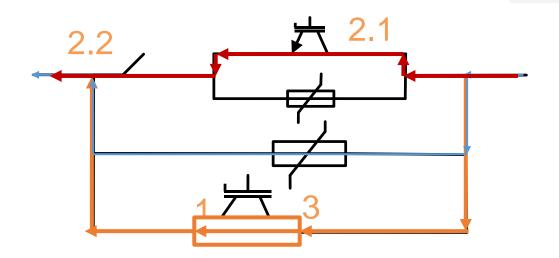

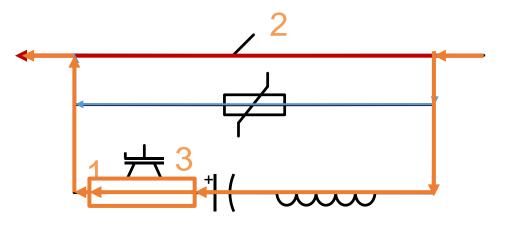

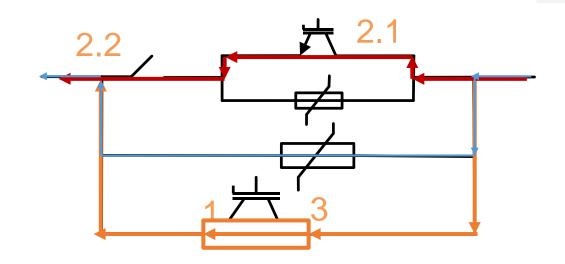

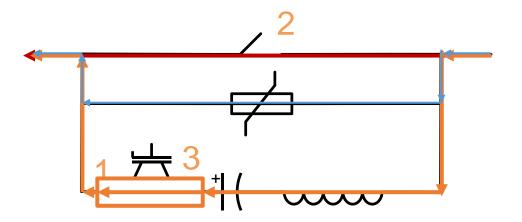

### **Breaker operating**

- 1. Close the auxiliary branch IGBT

- 2. Open the main branch switch

Hybrid breaker: *Open IGBT then Breaker* Mechanical breaker: us*ing LC oscillation branch Open Breaker at zero-crossing*

3. Open the auxiliary IGBT

IGBT current commutates to the surge arrestor Circuit response determined by the arrestor

4. Possible secondary breaker action

# **Breaker characteristics**

- Requires very high accuracy as a secondary breaker action may be required due to a re-closing failure

- The transient response happens in millisecond level, even in microsecond level

- High frequency oscillation is usually excited (several kHz)

# **Modelling Environment in RTDS**

• Substep (Novacor only)

| · · · · ·                | <br>Subste<br>Environm                 | ent                           | · · · | · · | · · ·    |

|--------------------------|----------------------------------------|-------------------------------|-------|-----|----------|

|                          | HIERA                                  | RCHY                          |       |     |          |

| Box Parameters           | Substep Options                        |                               |       |     |          |

|                          |                                        |                               |       |     |          |

| Name                     | Description                            | Value                         | Unit  | Min | Max      |

| Name                     | Box Name                               | Box1                          |       |     | <b>^</b> |

| FCOL                     | COLOR                                  | BLACK 💌                       |       |     |          |

| BCOL                     | COLOR                                  | RED                           |       |     |          |

| LW                       | LINE WIDTH                             | 1.0                           |       | 0.0 |          |

| DESC1                    | Description : Line #1                  | Substep                       |       |     |          |

| DESC2                    | Description : Line #2                  | on : Line #2 Environment      |       |     |          |

| IMAGE                    | mage file path (.gif or .jpeg)         |                               |       |     |          |

| IMAGE_RESIZE             | Resize image to fill box?              | NO 💌                          |       |     |          |

| EXCLUDE                  | Exclude contents from circuit          | de contents from circuit NO 🔽 |       |     |          |

| Туре                     | Choose type of hierarchy box SUBSTEP 💌 |                               | -     |     |          |

| Update Cancel Cancel All |                                        |                               |       |     |          |

• Smalldt (PB5, Novacor)

| · · ·                                                       |                                                           | VB1                | · · ·  | · · ·      | · · ·  | · · · |

|-------------------------------------------------------------|-----------------------------------------------------------|--------------------|--------|------------|--------|-------|

|                                                             | Г                                                         | tds_vsc_BRIDGE_BOX | [      |            |        |       |

| ENABLE                                                      | DIGITAL INPUT ENABLE                                      | GTAO OUTPUT CAP    | RDS IC | on Image O | ptions |       |

| BR                                                          | BRIDGE PARAMETERS BRIDGE PROCESSOR PARAMETERS             |                    |        |            |        |       |

|                                                             |                                                           |                    |        |            |        |       |

| Name                                                        | Descriptio                                                | n                  | Value  | Unit       | Min    | Max   |

| Name                                                        | Bridge Name VB1                                           |                    |        |            |        |       |

| Desc                                                        | Desc Description                                          |                    |        |            |        |       |

| dt_size                                                     | Request a small time-step size of: 1400 nanoSec 1400 3750 |                    |        | 3750       |        |       |

| rqnmp                                                       | nmp Requested Number of Processors: One 🔽 0 1             |                    |        | 1          |        |       |

| supprs Suppress WARNINGs, not ERRORs, about step size: NO 🔽 |                                                           |                    |        |            |        |       |

|                                                             |                                                           |                    |        |            |        |       |

| Update Cancel Cancel All                                    |                                                           |                    |        |            |        |       |

# **Modelling in RTDS Simulator**

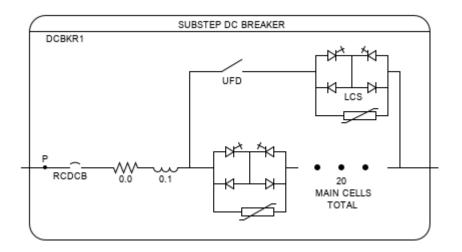

- Customized DC Breaker Model

- Built with Individual Component

Hybrid DC Breaker

Individual Combination

### **IGBT Switch model**

- Fast current conducting

- Block current immediately after turning-off

| PSCAD   | Resistive representation |

|---------|--------------------------|

| SUBSTEP | Resistive representation |

| SUBSILI | LC representation        |

| SMALLDT | LC representation        |

## **Mechanical Switch**

(Breaker model)

Block current immediately after turning-off

| PSCAD   | Resistive representation |

|---------|--------------------------|

| SUBSTEP | Resistive representation |

|         | LC representation        |

|         | Resistive representation |

| SMALLDT | (number limited)         |

|         | LC representation        |

### **Surge Arrestor**

- Determines the V-I characteristic after the IGBT open action

- Decides the response of the secondary breaker action

| PSCAD   | Piecewise V-I model        |  |

|---------|----------------------------|--|

| SUBSTEP | Piecewise V-I model        |  |

|         | Exponential V-I model      |  |

| SMALLDT | Piecewise V-I model        |  |

|         | Exponential V-I model      |  |

|         | (both with Interface Line) |  |

### **Modeling Experiences**

- Using LC switch representation on the power electronic switches (IGBT, Thyristor) has high possibility of giving wrong result (e.g., the failure of disconnection)

- Interface transmission line (Bergeron model) introduces additional voltage drop and current flowing path (virtual grounding capacitor), and possible high frequency oscillation

- An accurate arrestor characteristic is necessary as it directly determines the V-I characteristic (energy) and consequently, the accurate action of the secondary breaking

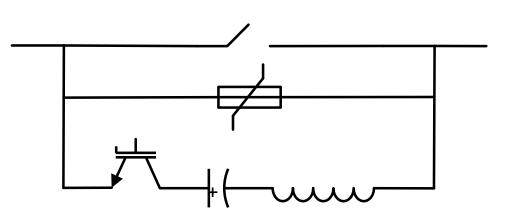

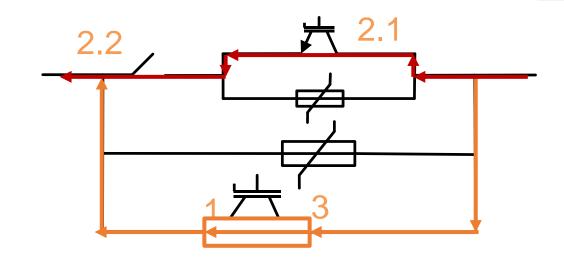

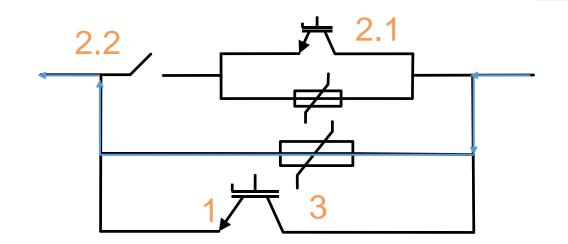

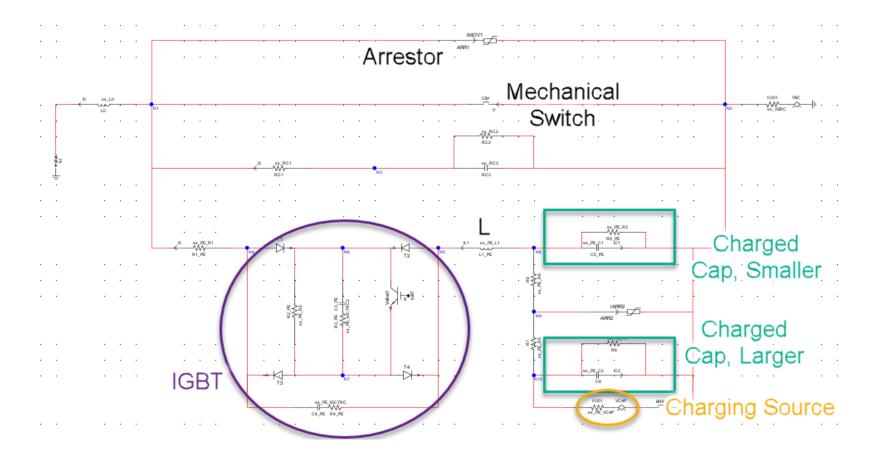

#### **Resonant Breaker I**

• Two charged capacitor (large and small)

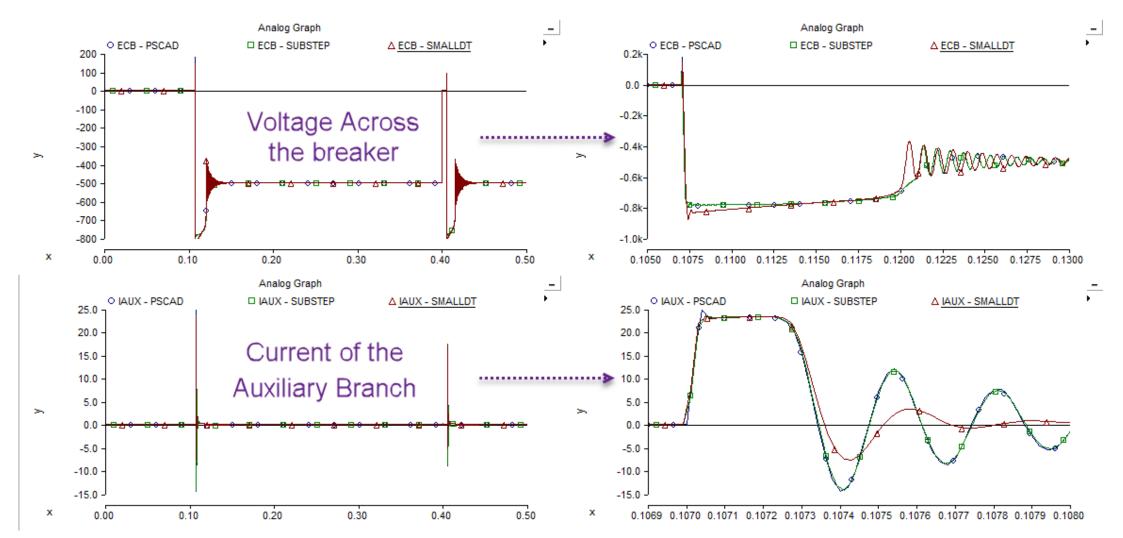

#### **Resonant Type I - Result**

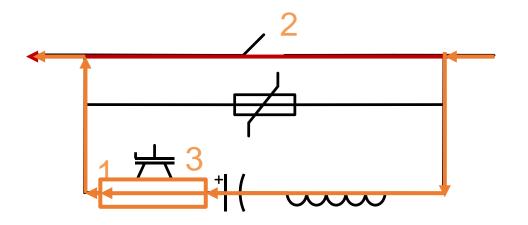

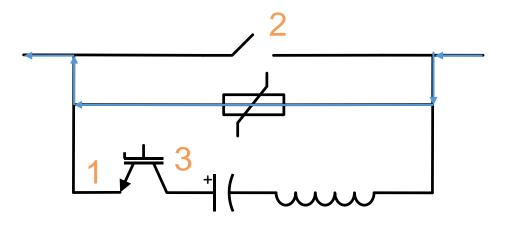

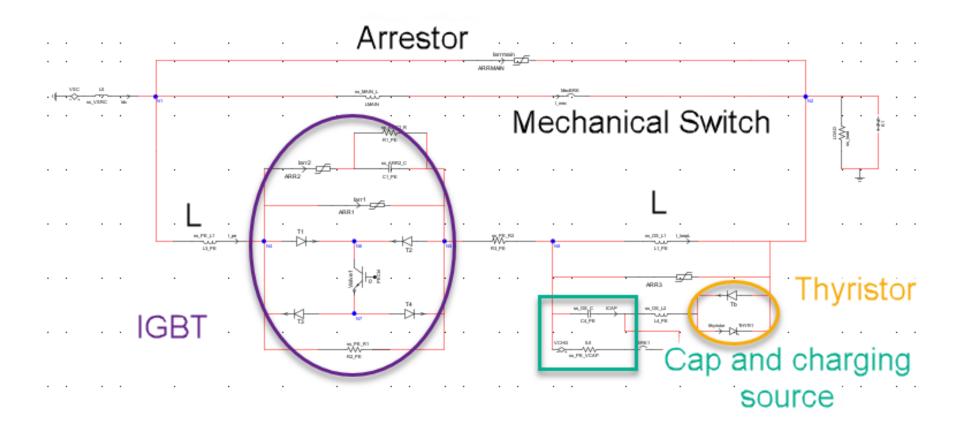

#### **Resonant Breaker II**

• One charged capacitor and use thyristor to restore capacitor energy

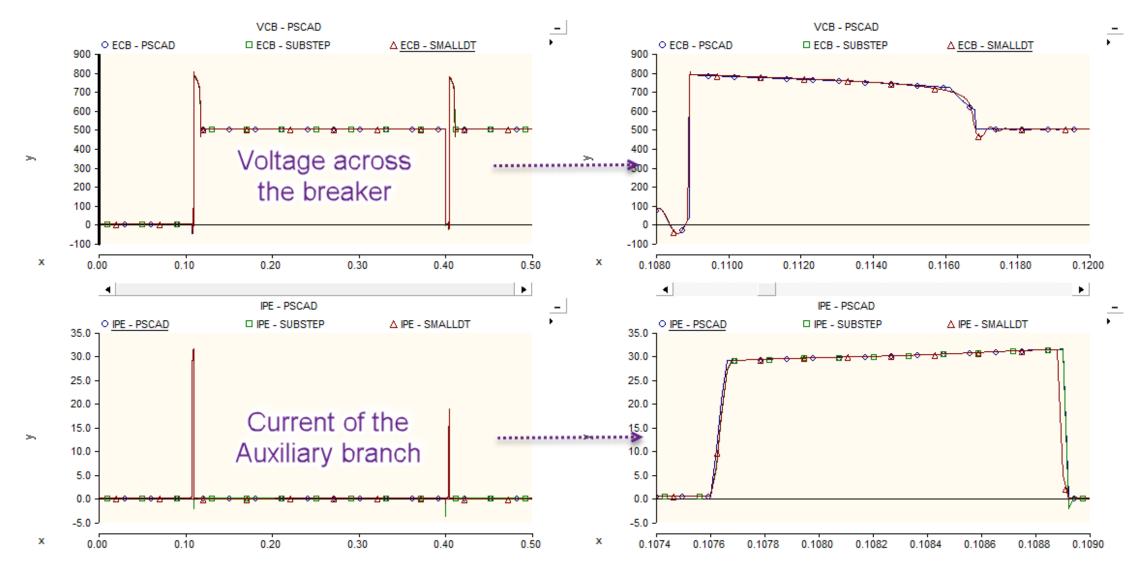

#### **Resonant Type II - Result**

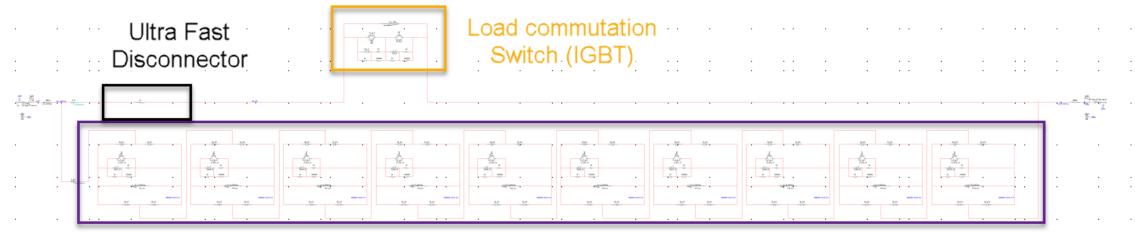

### **Hybrid Breaker**

• Modelling of the sub-modules in the Auxiliary branch

10 Sub-modules of the Auxiliary branch

52 Nodes; 64 IGBTs / Diodes; 11 Arrestors

Can be simulated in SUBSTEP with a time step of 4.167us

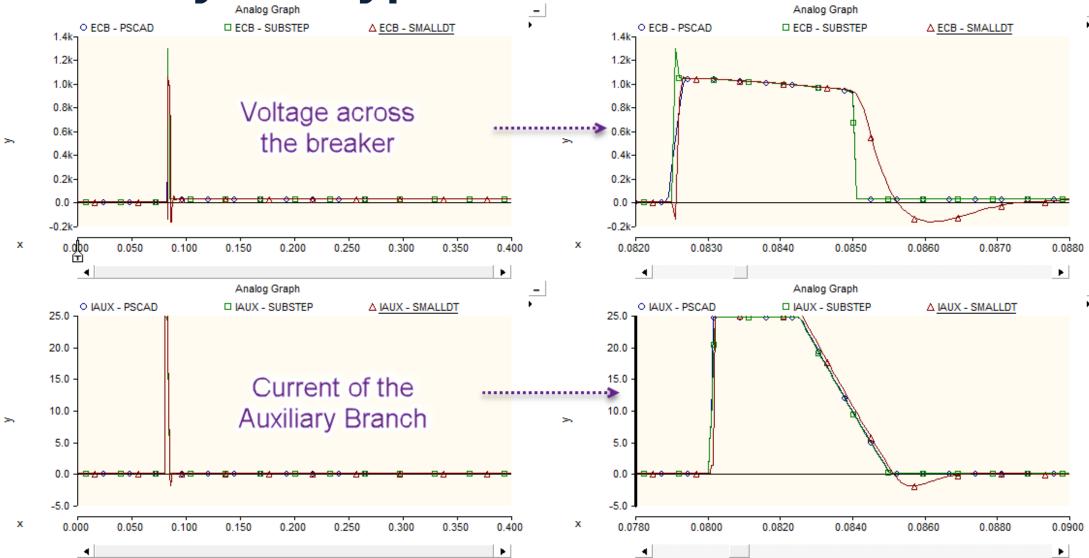

### Hybrid Type (in detail) - Result

#### Conclusion

- Substep environment can provide exactly the same model representation as in PSCAD/EMTDC, and consequently identical result waveforms

- Substep environment enables the DC breaker modelled in detail, e.g., into sub-modules for manufacture test

- Avoid of using the switches of LC representation is necessary in the dc breaker modeling, as there are components with current zero-crossing logic (e.g., a breaker)

#### Questions?