# Hardware-in-the-Loop Simulation of Distance Relay Using RTDS

Chenfeng Zhang, Vamsi K Vijapurapu, Anurag K Srivastava,

Noel N. Schulz, Jimena Bastos

<u>mailto:srivastava@ece.msstate.edu</u> Department of Electrical and Computer Engineering, Mississippi State University, Mississippi State, MS, 39762

**Keywords**—Real time simulation, Hardware-in-the-Loop, RTDS, SEL distance relay, power system protection

#### Abstract

Modeling and simulation of different conditions are needed for a better design of future Shipboard Power Systems (SPS). Research work at Mississippi State University (MSU) related to SPS protection aims to develop an adaptive protective controller, which can adapt to different protection schemes depending upon requirements. The first step in this research work is to develop the relay models. The developed relay model will be validated against a commercial relay using hardware-in-the-loop (HIL) simulation. HIL provides an opportunity for understanding the behavior and validating model of the physical device. This paper discusses HIL simulation for Schweitzer Engineering Laboratories (SEL) distance relay using the Real Time Digital Simulator (RTDS).

# 1. INTRODUCTION

Real time simulation is a commonly used tool for studying power system behavior in response to events. This kind of virtual test could uncover potential problems in advance. Corrective measures could then be taken before implementing the algorithm or logic in the real system. In HIL simulation, some of the components of the virtual power system are replaced with physical devices. HIL technology is one of the methods to understand nonlinear and dynamic behaviors of the system and helps in building and validating a model for physical devices. Authors in [1] presented experimental design for hardware-in-the-loop test and HIL test has been used for testing electric machines in [2]. Different approaches and preliminary design for HIL using National Instruments (NI) devices have been discussed in [3]. Real time digital simulator developments at Western Area Power Administration (WAPA) for testing a protective relay in real time have been presented in [4].

Shipboard Power Systems (SPS) have different characteristics from terrestrial power systems. It is important to investigate how best to adapt conventional protection schemes to SPS [5]. HIL provides a platform to test the performance of protection equipment under different conditions. HIL simulation may also be helpful for the designing the protection system for SPS. Real time assessment for SPS protection has been presented in [6], while the simulation of the electric ship in an efficient way Rudi Wierckx mailto:rpw@rtds.com RTDS Technologies Inc.

has been discussed in [7].

A Real Time Digital Simulator (RTDS) [5] is an effective tool for modeling and simulation of power and control systems. RTDS hardware employs high-speed DSP (digital signal processor) chips, operating in parallel, to compute simulation results with simulation step sizes as small as 2 microseconds. RTDS software called RSCAD (http://www.rtds.com/softover.htm) includes a graphical user interface and a detailed model library for power and control system components. Researchers at Mississippi State University (MSU) are working to develop adaptive protective controllers for SPS protection, which can adapt to different protection schemes depending upon requirements. The development of relay models for over-current, distance and differential protection is the first step in this process. To validate the performance of developed models, efforts have been made to develop hardware-in-the-loop simulation platform in VTB-RT, NI and RTDS [8,9]. Issues and challenges faced in using RTDS for HIL simulation of SPS have been discussed in [10]. Modeling of impedance relays using RTDS is presented in [11].

This paper describes the hardware-in-the loop testing of a SEL-421 (manufactured by Schweitzer Engineering Laboratories) high-speed transmission protection relay using a simulated power system. MSU researchers successfully connected the SEL 421 relay to an eight-bus power system modeled on the RTDS. Test results obtained for different types of faults are presented. Modeling of the relay is in progress and the performance of the developed relay model will be validated against the test results obtained from HIL test here.

# 2. POWER SYSTEM TEST CASE IN RSCAD

An eight-bus power system model consisting of the following components is used to test the relay.

- 1. 230kV AC Source;

- 2. A 203kV/230kV ( $\Delta$ -Y) Transformer;

- 3. 100 km long 'Traveling Wave' type Transmission Lines;

- 4. A 1200MVA, 15kV Synchronous machine

- 5. Speed Governor and Turbine

- 6. Static Exciter

- 7. Circuit Breakers.

- 8. CTs and PTs

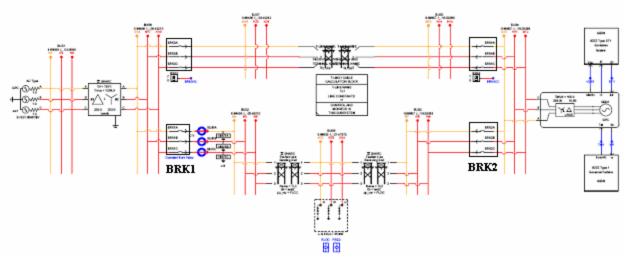

The test system has two parallel transmission lines between source and load as shown in fig.1.

Figure 1. 8-bus power system test case.

Breaker BRK1 is controlled by the physical SEL 421 relay, and breaker BRK2 is controlled by the logic designed in software. The CT and PT were modeled in detail to reflect real system characteristics.

#### 3. SEL -421 DISTANCE RELAY

The SEL-421 is a high-speed transmission line protective relay that includes single-pole tripping, three-pole tripping, reclosing with synchronism check, circuit breaker monitoring, circuit breaker failure protection, and seriescompensated line protection logic.

| Global Setings/Fn     Flobal Mn     Global Setings/Fn     Flobal Mn     Setings/Fn                                                                                                                                                                                                                                                   | Hel     | Import Egport   | ompare <u>S</u> earch  | Merge           | ⊆ору          | ≥>              | <≤          | Options | Eile |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------|------------------------|-----------------|---------------|-----------------|-------------|---------|------|

| Control Inputs     Control Input     Contro     Control Input     Control Input     Control Input     Control                                                                                                                                                                                                                                                   |         |                 | Trigger                | nd ER           | ogic a        | Trip L          | attings/En  |         |      |

| ■ Control Inputs       [211 OR 221 OR 55111         ■ Mar Boal Board       [RCOMM Communication Aided Trip (SELOGIC)         ■ Inder Source Status       [RCOMM Communication Aided Trip (SELOGIC)         ■ Settings Group Set instatus       [RCOMM Communication Aided Trip (SELOGIC)         ■ Frequency Estimation       [RCOMM File Resker 2 Manual Trip -BK1 (SELOGIC)         ■ Frequency Estimation       [RCOMM File Resker 2 Manual Trip -BK1 (SELOGIC)         ■ Frequency Estimation       [RCOM File Resker 2 Manual Trip -BK2 (SELOGIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                 |                        |                 | SELOGICI      | TR Trip (       |             |         |      |

| Interface Board<br>Settings Group Set<br>Settings Group Set<br>Data Rest<br>Frequency Estimatic<br>Time and Data Mail<br>Time Configurat<br>Dist Distance E<br>Settings Group 1<br>Time Data Mail<br>Time And Time Chase (SELOGIC)<br>Time Distance E<br>Status Distance Time Delay (SELOGIC)<br>Distance E<br>Status Distance Time Distance Time Delay (SelEDGIC)<br>Distance E<br>Status Distance E<br>Status Distance Time Distance Time Delay (SelEDGIC)<br>Distance E<br>Status Distance Time Distance Time Delay (SelEDGIC)<br>Distance E<br>Status Distance Time Delay (SelEDGIC)<br>Distance E<br>Status Distance Time Delay (SelEDGIC)<br>Distance E<br>Status Distance Time Delay (SelEDGIC)<br>Distance Time De | EB      |                 |                        | 61T             |               |                 |             |         | -    |

| Interface Boar     Settings Group Set     Data Reset     Data Reset     Data Reset     Data Reset     TRSOTE Switch-Ondo-Fault Trip (SELOGIC)     TRSOTE Switch-Ondo-Fault Trip (SELOGIC)     TRSOTE Switch-Ondo-Fault Trip A-Phase (SELOGIC)     Trip A-Phase (SEL                                                                                                                                                                                                                                                  |         |                 | USELOGICI              | ton Aided T     | 4 Communic    | TRCOM           |             |         |      |

| Settings Group Set Settings Group Set Soft Program Date Ma Date Protection Logic Date Protection Logic Date Protection Logic Tables Setting S                                                                                                                                                                                                                                              | EB      |                 | e (e a a e e e e e     |                 |               |                 |             |         |      |

| Frequency Eximation       [50P1 DOF M2P OR 22G         Time and Date Mail       The Direct Transfer Trip APhase (SELOGIC)         Image: Set 1       Image: Set 1         Image: Set 1       DTE Direct Transfer Trip B-Phase (SELOGIC)         Image: Set 1       Image: Set 1         Image: Set 1       DTE Direct Transfer Trip B-Phase (SELOGIC)         Image: Set 1       Image: Set 1         Image: Set 1       DTE Direct Transfer Trip B-Phase (SELOGIC)         Image: Set 1       Image: Set 1         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Transfer Trip D-Phase (SELOGIC)         Image: Set 1       DTE Direct Trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |                 |                        |                 |               | a second second |             |         |      |

| Time and Date Mate<br>Tansier d'Date Mate<br>Tansier d'Sarce Sel<br>DTA Direct Transfer Trip A-Phase (SELOGIC)<br>DTB Direct Transfer Trip B-Phase (SELOGIC)<br>DTB Direct Transfer Trip B-Phase (SELOGIC)<br>DTB Direct Transfer Trip B-Phase (SELOGIC)<br>DTD Direct Transfer Trip C-Phase (SELOGIC)<br>NA<br>BKTMTR Breaker 1 Manual Trip (SELOGIC)<br>DTC Direct Transfer Trip (SELOGIC)<br>DTC Trip (During Open Pole Trime Delay (cycles in 0.125 increments)<br>Derester 21<br>DTD Trip Unlatch Manual Trip -BK2 (SELOGIC)<br>TULD Trip Unlatch Manual Trip -BK2 (SELOGIC)<br>DTC Trip Unlatch Option<br>TULO Trip Unlatch Option<br>Drection Logic<br>TULD Trip Unlatch Prime Trip Unlatch Manual Trip -BK2 (SELOGIC)<br>TULD Trip Unlatch Prime Trip Unlatch Manual Trip (SELOGIC)<br>DTD Trip Unlatch Prime Trip Unlatch Manual Trip -BK2 (SELOGIC)<br>OTD Trip Unlatch Prime Trip Unlatch Manual Trip (SELOGIC)<br>DTD Trip Unlatch Prime Trip Unlatch Manual Trip (SELOGIC)<br>DTD Trip Unlatch Prime Trip Unlatch Manual Trip (SELOGIC)<br>DTD Trip Unlatch Prime Trip Unlatch Manual Trip (SELOGIC                                                                                                                                                                                                                                                                                                                                                 | Len I   |                 | LUGICJ                 |                 |               |                 |             |         |      |

| <ul> <li>I and V Source Sel</li> <li>Breaker Monitor</li> <li>Group 1</li> <li>The Conjugat</li> <li></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EB      |                 |                        |                 |               | 1               |             |         |      |

| <ul> <li>Breaker Monitor</li> <li>Breaker Monitor</li> <li>DTB Direct Transfer Trip B-Phase (SELOGIC)</li> <li>DTD Direct Transfer Trip D-Phase (SELOGIC)</li> <li>NA</li> <li>Breaker Monitor</li> <li>DTD Direct Transfer Trip D-Phase (SELOGIC)</li> <li>NA</li> <li>Breaker Monitor</li> <li>DTD Direct Transfer Trip D-Phase (SELOGIC)</li> <li>NA</li> <li>BKTMTB Breaker 1 Manual Trip (SELOGIC)</li> <li>DTO Direct BREAKER 2 Manual Trip (SELOGIC)</li> <li>DTO Direct BREAKER 2 Manual Trip (SELOGIC)</li> <li>DTD Direct BREAKER 2 Manual Trip -BK1 (SELOGIC)</li> <li>DTD Direct BREAKER 2 Manual Trip -BK1 (SELOGIC)</li> <li>DTD Direct Direct Transfer Trip D-Phase (SELOGIC)</li> <li>DTO Direct Trip D-Phase (SELOGIC)</li> <li>DTO Direct Trip D-Phase (SELOGIC)</li> <li>DTO D Trip D-Intip During Dpen Pole Time Delay (Secles in 0.125 increments)</li> <li>Strup 4</li> <li>DTO Tip D-Direct Transfer Trip D-Phase Time Delay (Secles in 0.125 increments)</li> <li>From Panel</li> <li>DURAD SET MI Trip Duration Time Delay (secles in 0.125 increments)</li> <li>Expose 5</li> <li>Group 5</li> <li>DUFAD 50 PT MI Trip Duration Time Delay (secles in 0.125 increments)</li> <li>Expose 5</li></ul>                                                                                                                                                                                                                                         | and and |                 | SELOGIC)               | rip A-Phase     | ct Transfer   |                 |             |         |      |

| <ul> <li>Group 1</li> <li>DTB Direct Transfer Trip B-Phase (SELOGIC)</li> <li>NA</li> <li>DTB Direct Transfer Trip B-Phase (SELOGIC)</li> <li>NA</li> <li>DTB Direct Transfer Trip C-Phase (SELOGIC)</li> <li>Phase Dorts</li> <li>Phase Dorts</li> <li>BKMTR Breaker 1 Marual Trip (SELOGIC)</li> <li>Directora</li> <li>Director</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EB      |                 |                        |                 |               | INA             |             |         |      |

| Check Configurat,<br>Phase Dirt<br>Phase Dirt<br>Phase Dirt<br>Phase Dirt<br>Phase Dirt<br>Phase Dirt<br>Phase Dirt<br>Phase Dirt<br>Distance E<br>Studt-Nort<br>Out of Ster<br>Phase Int<br>Out of Ster<br>Phase Int<br>Phase Int                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                 | SELOGIC)               | rip B-Phase     | ect Transfer  |                 | ******      |         |      |

| Precedure Control of the set                                                                                                                                                                                                                                                  | EB      |                 |                        |                 |               | NA              |             | Set 1   | ė-   |

| Phase Diet     Phase Diet     Phase Diet     Start TR Breaker 1 Manual Trip (SELDGIC)     Distance E     Switch-Ont     Out of Stee     Out of Stee     Out of Stee     Switch-Ont     Out of Stee     Out of St                                                                                                                                                                                                                                                  |         |                 | SELOGIC)               | rip C-Phase     | ct Transfer   | DTC Dire        |             |         |      |

| Ground Dis     BK1MTR Breaker 1 Manual Tip (SELOGIC)     COT OF PSP PUL     GOTOR FPS PUL     GOTOR FPS PUL     Switch-Ort     GOTOR FPS PUL     BK2MTR Breaker 2 Manual Tip (SELOGIC)     ULdr5 Step     Load Encr     ULTR Unlatch Tip (SELOGIC)     TREGOR     COLOR VILTR Unlatch Manual Tip -8K1 (SELOGIC)     ULTR Unlatch Manual Tip -8K1 (SELOGIC)     ULTR Unlatch Manual Tip -8K2 (SELOGIC)     DOT TIP DURING Open Pole Time Delay (cycles in 0.125 increments)     Synchronis     Recksing-     Denael M     Group 5     Group 5     Group 5     Front Panel     DURING 2PT Min Tip Duration Time Delay (cycles in 0.125 increments)     IOURING 2PT Min Tip Duration Time Delay (cycles in 0.125 increments)     IOURING 2PT Min Tip Duration Time Delay (cycles in 0.125 increments)     Group 5     Group 5     Group 6     Automation Logic     Dutputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | EB      |                 |                        |                 |               | NA              |             |         |      |

| Objectson E      O                                                                                                                                                                                                                                                  |         |                 | 1.0610                 | anual Trin (9   | Breaker 1     | BK1MTB          |             |         |      |

| Switch-Ohrt     SWitch-Oh                                                                                                                                                                                                                                                  | EB      |                 | (Louio)                | rancial rinp (c |               |                 |             |         |      |

| UUL of Steel     UUL TR Unlatch Trip (SELDGIC)     Freidaul G     ULTR Unlatch Trip (SELDGIC)     Trib Dver     ULTR Unlatch Manual Trip -8K1 (SELDGIC)     ULMTR Unlatch Manual Trip -8K1 (SELDGIC)     ULMTR Unlatch Manual Trip -8K2 (SELDGIC)     ULMTR 2 U                                                                                                                                                                                                                                                  | LD      |                 | 1.0010                 |                 |               |                 |             |         |      |

| Phase Inst     ULTR Unlatch Trip [SELOGIC]     TRGTR     ULTR1 Unlatch Manual Trip-8K1 (SELOGIC)     TRGTQ     ULTR1 Unlatch Manual Trip-8K1 (SELOGIC)     Directional     Pole Deen     POTT/DCI     Directional     POTT/DCI     POTT/DCI     Directional     POTT/DCI                                                                                                                                                                                                                                                     |         |                 | LUGICJ                 | tanual Trip (s  | Breaker 2     |                 | Jut-of-Step | 0 0     |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EB      |                 |                        |                 |               | INA             |             |         |      |

| Negatives     ULATRI Unlatch Manual Trip-BK1 (SELOGIC)     ULATRI Unlatch Manual Trip-BK1 (SELOGIC)     ULATRI Unlatch Manual Trip-BK1 (SELOGIC)     ULATRI Unlatch Manual Trip-BK2 (SELOGIC)     ULATRI Unlatch Option     Range = 2.000 - 8000.000     TULC Trip Unlatch Option     Range = 2.000 - 8000.000     ULputs     Front Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |         |                 |                        | ELOGIC)         | nlatch Trip ( | ULTR U          |             |         |      |

| JUMTRI Unlach Manual Tip-BK1 (SELOGIC)     JUMTRI Unlach Manual Tip-BK2 (SELOGIC)     JULTRI Unlach Manual Tip-BK2 (SELOGIC)     JULTRI Z Unlach Manual Tip-BK2 (SELOGIC)     JULTRI S UNLACH MANUAL                                                                                                                                                                                                                                                  | EB      |                 |                        |                 |               | TRGTR           |             |         |      |

| Directional     Direction                                                                                                                                                                                                                                                  |         |                 | (SELOGIC)              | nual Trip -BK   | Unlatch M     | ULMTR1          |             |         |      |

| POTT/OCI     POTT/OCI     POTT/OCI     DOLTING Officient Market Mp One (OccOdd)     DOLTING Officient Market Mp One (OccOdd)     DOLTING Officient Market Mp One (OccOdd)     TOPD Trip During Open Pole Time Delay (cycles in 0.125 increments)     Zono Range - 2000 - 8000.000     TULD Trip Unlach Option     Potection Logic     Demand M     Group A     Group A     Group 5     Group A     Automation Logic     Outputs     Front Panel     TOPD Trip During Open Pole Time Delay (cycles in 0.125 increments)     TOPD Trip During Open Pole Time Delay (cycles in 0.125 increments)     TOPD Trip During Open Pole Time Delay (cycles in 0.125 increments)     TOPD Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Trip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Tip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Tip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Tip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Tip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Tip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Tip During Time Delay (cycles in 0.125 increments)     TOURID SPT Min Tip During Time Delay (cycles in 0.125 incre                                                                                                                                                                                                                                                  | EB      |                 | (C1)                   | AB1 AND 52      | AA1 AND 5     | NOT(52          |             |         |      |

| POTTACL     P                                                                                                                                                                                                                                                  |         |                 | (SELOGIC)              | nual Trin -BK   | Linlatch M    | ULMTB2          | ole Open    | F       |      |

| DUS Ing S     Destant 1                                                                                                                                                                                                                                                    | EB      |                 | ()                     |                 |               |                 |             |         |      |

| Birester 21<br>Synchronis         2000         Range = 2.000 - 8000.000           Birester 21<br>Synchronis         TULD Trip Unlatch Option           Protection Logic 1         Select 1.4           Frigt Looses         Select 1.4           Group 3         Select 1.4           Group 3         Frigt Looses           Group 3         FOR tection Logic 1           Group 4         FOR SP Zone 2. Dir. Neg. Seg. /Res. Overcurrent SPT           Group 5         FOR SP Zone 2. Dir. Neg. Seg. /Res. Overcurrent SPT           Group 5         FOR SP Zone 2. Dir. Neg. Seg. /Res. Overcurrent SPT           Group 5         FOR SP Zone 2. Dir. Neg. Seg. /Res. Overcurrent SPT           Group 5         FOR The Trip Unlation Time Delay (cycles in 0.125 increments)           Group 5         FOR Panel           Front Panel         Range = 2.000 - 8000.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | (incremente)    | Delau foueles in 0.12  | on Role Time    | in During Or  | ( <b>8</b> .)   |             |         |      |

| Synchronis     S                                                                                                                                                                                                                                                  |         | increments)     |                        |                 |               |                 |             |         |      |

| Brectoria         Tocs mp Offset register           • Friesbages         Select: 1-4           • Friesbages         ZGISPZ one 2 Ground Distance Time Delay SPT           • Group 2         • N           • Group 3         • O'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                 | 0.000                  |                 |               | a second second |             |         |      |

| Demand M         Z2015 P2 Zone 2 Ground Distance Time Delay SPT           Protection Logic 1         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 5         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 5         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 5         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 6         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 5         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 6         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 5         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 6         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 5         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 6         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 6         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 6         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 6         F02 GSP Zone 2 Dir. Neg. Seq. Res. Overcurrent SPT           Group 7         Range - 2 000 - 8000 000           Front Panel         Range - 2 000 - 8000 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                 |                        |                 |               |                 |             |         |      |

| Protection Logic 1     Group 2     Group 3     Group 5     Group 6     Group 5     Group 6     Group 6     Group 5     Group 5     Group 6     Group 5     Group 6     Group 7     Group 6     Group 7     Group 7     Group 7     Group 8     Gr                                                                                                                                                                                                                                                  |         |                 |                        |                 |               | 1.00            | emand M     | - C     |      |

| Computer Logic 1     Comp                                                                                                                                                                                                                                                  |         |                 |                        |                 | P Zone 2 G    |                 |             |         |      |

| Group 3         Drup 3 <thdrup 3<="" th=""> <thdrup 3<="" th=""> <thdrup 3<="" t<="" td=""><td></td><td></td><td></td><td></td><td></td><td></td><td>n Logic 1</td><td></td><td></td></thdrup></thdrup></thdrup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                 |                        |                 |               |                 | n Logic 1   |         |      |

| Group 4     Group 5     Group 5     Group 6     Group 6     Group 6     Group 6     Group 6     Automation Logic     Outputs     Front Panel     T2000     T2000     T2000     T2000     T2000     Group 6     Group 6     Group 6     Group 6     Group 6     Group 7                                                                                                                                                                                                                                                     |         |                 |                        |                 | P Zone 2 D    |                 |             |         |      |

| Group 5     Group 6     Automation Logic     Outputs     For Nanel     ToUR3D 3PT     Range = 2.000 - 8000.000     Range = 2.000 - 8000.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                 | N                      | (•              |               | ( Y             |             |         |      |

| Automation Logic     Dutputs     For Ranel     ToUR3D 3PT Min Trip Duration Time Delay (cycles in 0.125 increments)     12.000     Range = 2.000 - 8000.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 125 increments) | ne Delay (cycles in 0. | ip Duration T   | SPT Min T     | TDUR1D          |             |         |      |

| Outputs     Front Panel     I2.000     Range = 2.000 - 8000.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                 | 0.000                  | = 2.000 - 80    | Rang          | 6.000           |             |         |      |

| Outputs         12.000         Range = 2.000 - 8000.000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | 125 increments) | ne Delay (cycles in 0. | p Duration T    | 3PT Min T     | TDUR3D          | ogic        |         |      |

| - O Front Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                 |                        |                 |               |                 |             |         |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |                 |                        |                 |               |                 |             |         | 0    |

| Pushbuttons     E3PT Three-Pole Trip Enable (SELOGIC)     Target LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | EB      |                 | 56(6)                  | Chaple (SEL     | CON DIE TH    | -               |             |         |      |

| Selectable Screen: E3PT1 Breaker 1 3PT (SELOGIC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |                 |                        |                 |               |                 |             |         |      |

Figure 2. ACSELERATOR settings for SEL 421

Settings for the SEL-421 relay can be set based on power system characteristics using the ACSELERATOR software as shown in fig. 2. [12]

#### 4. HARDWARE SETUP AND CONTROL LOGIC

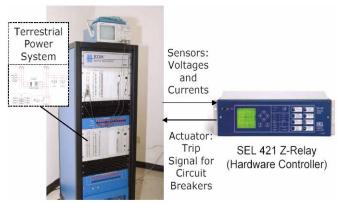

Fig. 3 shows the interfaced signals between the relay and the RTDS. The relay senses the voltages and currents from the RTDS system, and in case of any fault, it sends out the trip and reclose signals to the simulated circuit breakers in the power system.

Figure 3. HIL setup using RTDS for SEL 421

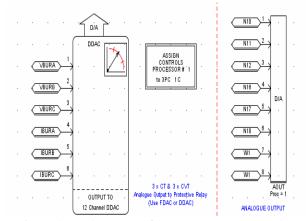

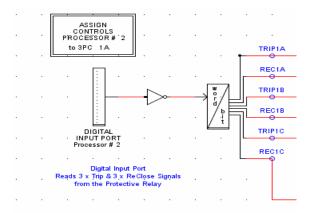

Fig. 4 shows how simulated voltage and current signals are sent to D/A converters on the RTDS. The analog signals are then connected to the relay's inputs. SEL relays can be tested with low-level signals or high-level signals. RTDS has the ability to be directly connected to the relay using a low-level signal. An amplifier can be used, if the relay needs to be tested with a high-level signal. In this research, low-level signals were used to interface with the relay. Trip and reclose signals from the relay are interfaced to the RTDS via digital input ports. Fig. 5 shows how the digital input signals are interfaced in the simulation.

Figure 4. Analog output from power system to relay

Figure 5. Digital signal from relay to power system

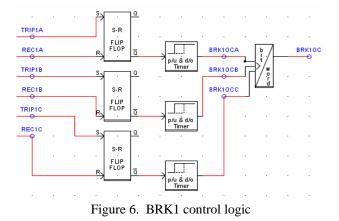

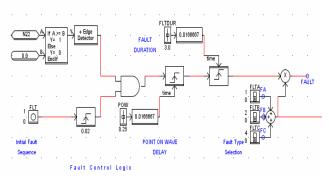

Breaker (BRK1) is directly controlled by the signal received from the physical relay for each phase. Control logic to operate the breaker based on signals from the relay is shown in fig. 6. Figure 7 shows fault control logic to simulate the different types of faults. For a single-phase line to ground fault, BRK1 and BRK 2 should open and reclose once the fault clears automatically for each phase. In the case of a two-phase line to ground fault, all 3 phases of BRK1 and BRK2 should open but should not reclose automatically even after the fault clears.

Figure 7. Fault control logic for eight-bus power system

## 5. SIMULATION RESULTS

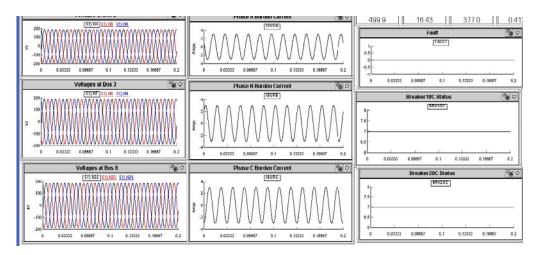

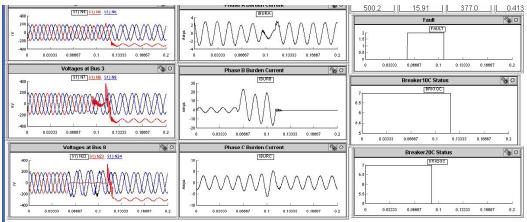

Single phase line to ground and two-phase line to ground fault were simulated at a 50% distance on the transmission line in the eight-bus test case. Simulation results obtained for these faults on different phase have been presented here. Simulation results show expected results and successful operation of commercial relay. These results will be used to validate the developed relay model in future research work. Figure 8 shows the voltage, current waveforms and breaker status without any fault. The simulation results show that 'FAULT' signal is equal to 0, which means no fault at this time and the breakers BRK1OC (BRK1) and BRK2OC (BRK2) statuses are equal to 7, which is "111" in the binary form. The first bit of binary form stands for the breaker status for phase C, the second one for phase B and the third one for phase A. "1" means that the breaker is closed, and "0" means open. Therefore, for no fault, all breakers are closed.

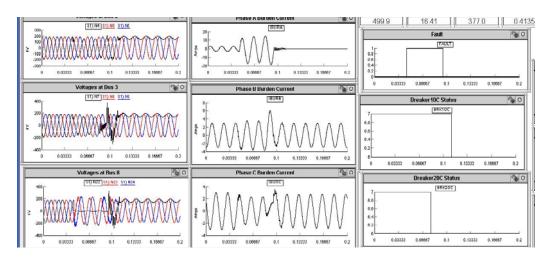

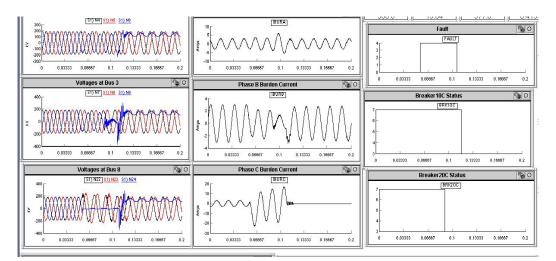

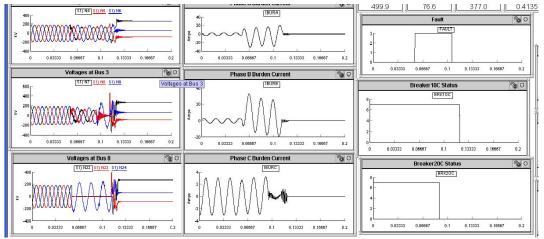

Simulation results for single-phase fault on 'phase A' are shown in fig. 9. Current on 'phase A' becomes high when the fault is initiated and becomes zero when the relay operates and the breaker opens. In this case the value of the "FAULT" signal is equal to 1. The breaker BRK1OC would open about 1.7 cycles after the fault, and the breaker BRK2OC would open after approximately two cycles after the fault. Figures 10 and 11 show similar results for a single-phase fault on 'phase B' and 'phase C'. The transient response in case of two-phase line to ground fault is shown in fig. 12. Fault on 'phase A and phase B' to ground was simulated. Relay signals open the breakers and the current becomes zero for all 3 phases. The breakers will not reclose until the manual reclose button is pressed. Simulation results for faults on 'phase A and phase C' to ground and also 'phase B and phase C' to ground were obtained in a similar manner but have not been shown here due to space limitation in paper.

Figure 8. Power system without fault

Figure 9. Single-phase fault on phase A

Figure 10. Single-phase fault on phase B

Figure 11. Single-phase fault on phase C

Figure 12. Two-phase fault on phase A and phase B

## 6. SUMMARY

Hardware-in-the-loop simulation to test a SEL 421 distance relay has been presented in this paper. Hardware setup, control logic and power system test case development have been discussed in detail. Simulation results for single-phase line to ground and two-phase line to ground faults have been presented. Hardware-in-the-loop tests for differential relay and over-current relay using RTDS are part of the current research activities at Mississippi State University (MSU) in an effort to develop an adaptive protective relay for Shipboard Power System (SPS). Modeling of different types of relays is in progress.

#### 7. ACKNOWLEDGEMENT

Authors are thankful to DoD DURIP Grant No. N000140610752 and ONR grant no. N00014-02-1-0623 for

supporting this research work.

#### References

- J. Wu and N. N. Schulz, "Experimental Design for Remote Hardware-In-the-Loop testing," *Proceedings of ASNE Reconfiguration and Survivability Symposium*, Jacksonville, Florida, Feb. 2005.

- [2] S. Ayasun, S. Vallieu, R. Fischl, and T. Chmielewski, "Electric machinery diagnostic/testing system and power hardware-in-the-loop studies," 4th *IEEE International Symposium on Diagnostics for Electric Machines*, Aug. 2003, pp. 361–366

- [3] Jian Wu, Yong Cheng, Anurag K Srivastava, Noel N. Schulz, Herbert L. Ginn III "Hardware-in-the-Loop Test for Power System Modeling and Simulation," *IEEE PES Power Systems Conference and Exposition, PSCE, 2006* Oct. 29-Nov. 1 2006, pp. 1892 – 1897.

- [4] M. Kezunovic, M. McKenna, "Real-time digital simulator for protective relay testing", *IEEE Computer Applications in Power*, Vol. 7, Issue 3, July 1994, pp. 30 – 35.

- [5] RTDS Technologies, http://www.rtds.com/index.html

- [6] A.Mackay, S.Galloway, C.Booth, and J.R.Mcdonald, "Real-Time Assessment of Relay Protection Schemes on Integrated Full Electric Propulsion Systems", *Proceedings of IEEE Electric Ship Technologies Symposium*, 25-27 July, 2005, pp. 230-236.

- [7] Roy E. Crosbie, "Low-Cost, High-Speed, Real-Time Simulation for Electric Ship Power Systems", *Proceedings of IEEE Electric Ship Technologies Symposium*, 25-27 July, 2005, pp. 46-47.

- [8] Yujie Zhang, Jimena Bastos, Noel N. Schulz and Daxa Patel, "Modeling and Testing of Protection Devices for SPS using MATLAB/Simulink and VTB," *Proceedings of the IEEE Electric Ship Technologies Symposium*, 2007, June 2007, in press.

- [9] Sunil Palla, Anurag K Srivastava, and Noel N. Schulz, "Hardware-in-the-loop test for relay model validation," *Proceedings of the IEEE Electric Ship Technologies* Symposium, 2007, June 2007, in press.

- [10] W. Ren, and M.Steurer, "Progress and Challenges in Real Time Hardware-in-the loop Simulations of Integrated Ship Power system", Proceedings of *IEEE power Engineering Society General Meeting*, 12-16 June, 2005, pp. 534-537

- [11] D. S Ouellette, W.J. Geisbrecht, R.P. Wierckx, and P.A. Forsyth, "Modeling an impedance relay using a real time digital simulator" 8<sup>th</sup> IEE International Conference on Developments in Power System Protection, 2004. vol. 2, 5-8 April 2004 Page(s):665 - 668 Vol.2

- [12] Schweitzer Engineering Laboratories (SEL) manual for protective relays, available on website: <u>http://www.selinc.com</u>.

#### **Biography**

**Chenfeng Zhang** has been pursuing her master's degree since 2006 in Electrical and Computer Engineering at Mississippi State University (MSU). She received BSEE from Chengdu University of Technology and MSEE from University of Electronic and Science of Technology in China. Her fields of interest include modeling and simulation and protection in power systems.

Vamsi K Vijapurapu was born in Andhra Pradesh, India in the year 1985. He received his Bachelor of Technology (B.Tech) Degree in Electrical & Electronics Engineering from Chaitanya Engineering College, Andhra Pradesh, India in 2006. He is presently pursuing his Master's Degree at Mississippi State University (MSU) in the Electrical & Computer Engineering Department. He is a member of the IEEE and his research interests include power system protection, modeling and simulation and real time analysis.

**Anurag K. Srivastava** received his Ph.D. degree from Illinois Institute of Technology (IIT), Chicago, in 2005, M. Tech. from Institute of Technology, India in 1999 and B. Tech. in Electrical Engineering from Harcourt Butler Technological Institute, India in 1997. He is working as Assistant research professor at Mississippi State University since September 2005. Before that, he worked as research assistant and teaching assistant at IIT, Chicago, USA and as Senior Research Associate at Electrical Engineering Department at the Indian Institute of Technology, Kanpur, India as well as Research Fellow at Asian Institute of Technology, Bangkok, Thailand. His research interest includes real time simulation, power system modeling, power system security, power system deregulation and artificial intelligent application in power system. Dr. Srivastava is member of IEEE, IET, Power Engineering Society, Sigma Xi and Eta Kappa Nu. He is recipient of several awards and serves as reviewer for IEEE Transactions, international journals and conferences.

Jimena L. Bastos received her B.S. in Electronics Engineering from the National University of Engineering (Universidad Nacional de Ingenieria), Lima, Peru, in December 2000. After graduating, she worked as a junior design engineer in a major Peruvian telecommunications company. She received her M.E. and Ph.D. degrees from the University of South Carolina, Columbia, SC in August 2003 and 2005, respectively. Her dissertation research focused on the application of modeling and simulation techniques in electrical drives and power electronics control applications. As a result of her graduate research work, she holds two invention disclosures for creating two software tools for computer-aided design of circuit-based models and nonlinear controllers for power engineering applications. She joined Mississippi State University as a Assistant Research Professor in August 2006, after spending one year in a post-doctoral position at the University of South Carolina. At her current position, she is currently combining her research activities in power engineering with her teaching activities.

**Noel N. Schulz** received her B.S.E.E. and M.S.E.E. degrees from Virginia Polytechnic Institute and State University in 1988 and 1990, respectively. She received her Ph.D. in EE from the University of Minnesota in 1995. She has been an Associate Professor in the ECE department at Mississippi State University since July 2001. She currently holds the TVA endowed professorship in power systems engineering. Her research interests are in computer applications in power system operations including artificial intelligence techniques. She is a NSF CAREER award recipient. She has been active in the IEEE Power Engineering Society and is serving as Secretary for 2004-2007. She was the 2002 recipient of the IEEE/PES Walter Fee Outstanding Young Power Engineer Award. Dr. Schulz is a member of Eta Kappa Nu and Tau Beta Pi.

**Rudi Wierckx** received B.Sc (EE) 1983 and M.Sc (EE) 1985 degrees from the University of Manitoba. Between 1985 and 1993, he was employed by the Manitoba HVDC Research Center, working on the development of the Real-Time Digital Simulator (RTDS). In 1993 he left the Research Center to form RTDS Technologies Inc. and is currently a director of that company.